Р.Т. Газиева,

А.М. Нигматов

Э.О. Бозоров

Э.О. Озодов

# ЦИФРОВОЕ УПРАВЛЕНИЕ

Учебное пособие

для студентов специальности

5311000-«Автоматизация и управление технологических

процессов и производств (в водном хозяйстве)»

ТАШКЕНТ

2020

**МИНИСТЕРСТВО ВЫСШЕГО И СРЕДНЕГО СПЕЦИАЛЬНОГО

ОБРАЗОВАНИЯ РЕСПУБЛИКИ УЗБЕКИСТАН**

**ТАШКЕНТСКИЙ ИНСТИТУТ ИНЖЕНЕРОВ ИРРИГАЦИИ

И МЕХАНИЗАЦИИ СЕЛЬСКОГО ХОЗЯЙСТВА**

---

**Р.Т. Газиева, А.М. Нигматов,

Э.О. Бозоров, Э.О. Озодов**

# **ЦИФРОВОЕ УПРАВЛЕНИЕ**

**Учебное пособие

для студентов специальности**

**5311000-«Автоматизация и управление технологических процессов

и производств (в водном хозяйстве)»**

**ТАШКЕНТ

2020**

*Данное учебное пособие утверждено и рекомендовано к публикации в соответствии с приказом Министерства высшего и среднего специального образования Республики Узбекистан от 28 декабря 2020 года за № 676.*

Регистрационный номер 676-364

УДК \_\_\_\_\_

### **Аннотация**

Учебник подготовлен в соответствии с учебными планами дисциплины «Цифровое управление». В книге изложены теоретические и практические вопросы, знание которых требуется для создания современных цифровых систем управления в сельском и водном хозяйстве.

Учебное пособие предназначено для студентов высших учебных заведений, обучающихся по направлению специальности 5311000-«Автоматизация и управление технологических процессов и производств (в водном хозяйстве)».

Учебное пособие может использоваться и для обучения по другим аналогичным дисциплинам в высших учебных заведениях.

**Рецензенты:**

---

---

---

Р.Т. Газиева, А.М. Нигматов, Э.О. Бозоров, Э.О. Озодов

/ ЦИФРОВОЕ УПРАВЛЕНИЕ /

Учебное пособие, Ташкент – 2020 г., 178 стр.

## **Аннотация**

Ўкув кулланма “Ракамли бошкариш” фанининг ўкув режалари асосида тайёрланган. Китобда сув хўжалигида замонавий ракамли бошкариш тизимларини қуриш учун билиш талаб қилинадиган назарий ва амалий саволлар баён қилинган. Хусусан, ТЖАБТ таркибидағи ракамли бошкарув элементларининг асосий тушунчалари, микропроцессорли бошкарув тизимлари ва уларни қуриш тамойиллари тўғрисида, кишлок ва сув хўжалиги тизимларда технологик жараёнларни бошқарувини автоматлаштириш ва ахборот таъминоти масалалари тўғрисида, ракамли бошқарув тизимлари концепцияси негизида замонавий автоматлаштирилган тизимни қуриш тўғрисида баён қилинган.

Ўкув кулланма олий ўкув юртларининг 5311000 – “Технологик жараёнлар ва ишлаб чиқаришни автоматлаштириш ва бошқарув (сув хўжалигида)” йўналиши бўйича ўқитилаётган талабалар учун мўлжалланган.

Шунингдек, ушбу ўкув кулланма олий ўкув юртларининг шунга ўхшаш фанлари бўйича таълим беришда ҳам кўлланилиши мумкин.

## **Annotation**

The manual was prepared in accordance with the curriculum of the discipline "Digital control ". The book contains theoretical and practical issues, knowledge of which is required to create modern digital control systems in agriculture and water management. In particular, the basic concepts and definitions of digital APСS systems, microprocessor control systems and the principles of their construction, the tasks of information support and automation of technological processes in agriculture and water management, the life cycle of creating a modern automated system based on digital systems using microcontrollers, signal processors, and specialized microcircuits such as codecs, modems, analog-to-digital or digital-to-analog converters.

The textbook is designed for students of higher educational institutions studying in the specialty 5311000- "Automation and control of technological processes and production (in water management)".

The textbook can be used for teaching in other similar disciplines in higher educational institutions.

## Содержание

|                                                                                                                        |     |

|------------------------------------------------------------------------------------------------------------------------|-----|

| Введение                                                                                                               | 9   |

| 1. Основные понятия. Цифровые устройства, структура                                                                    | 10  |

| 2. Области применения цифровых микросхем                                                                               | 12  |

| 3. Сумматоры                                                                                                           | 16  |

| 4. Схема строения и принцип работы компоратора                                                                         | 32  |

| 5. Элементы хранения - триггеры, асинхрон и синхрон<br>RS-триггеры. D-триггер, Т-триггер и универсальный<br>JK-триггер | 39  |

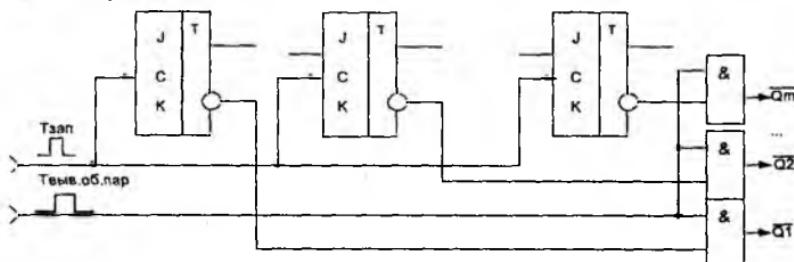

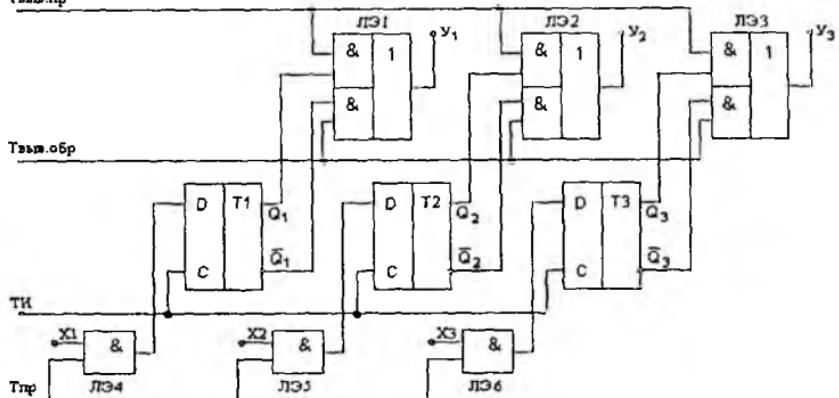

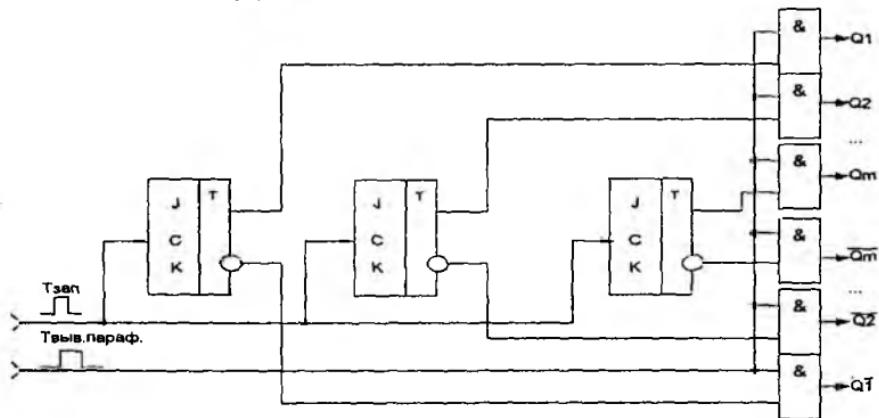

| 6. Регистры. Параллельная и последовательная работа ре-<br>гистров                                                     | 63  |

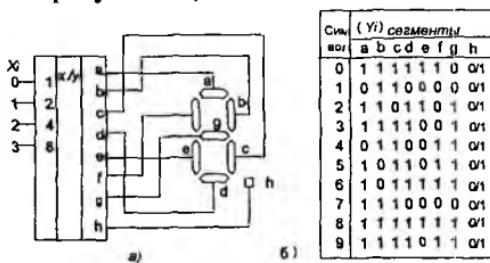

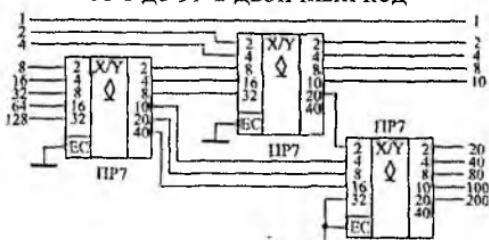

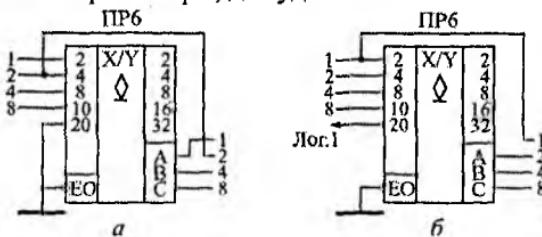

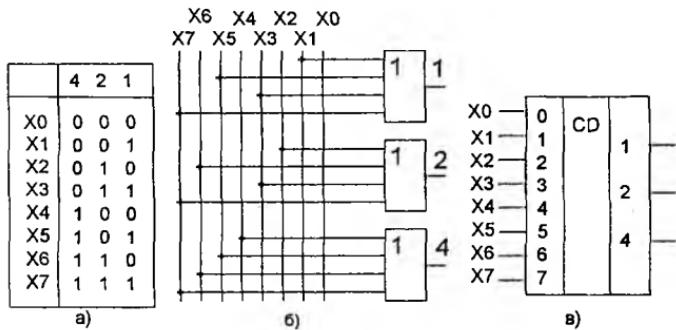

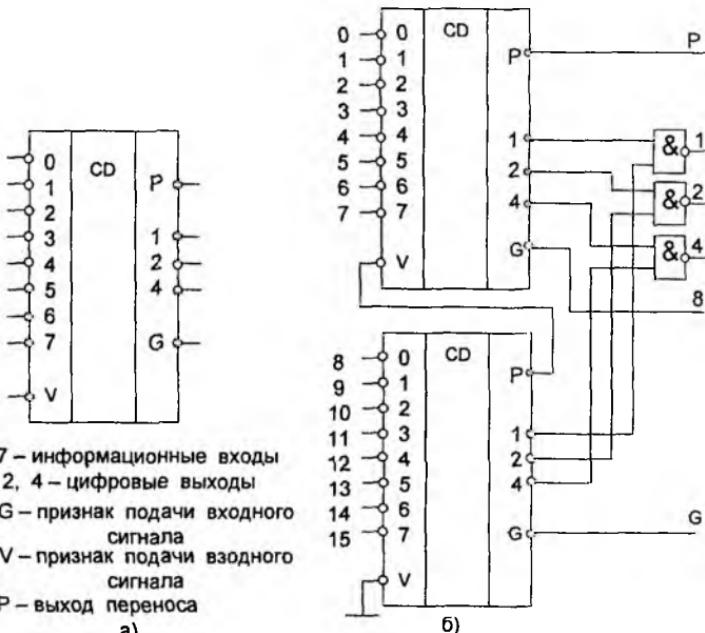

| 7. Кодопреобразователи.                                                                                                | 87  |

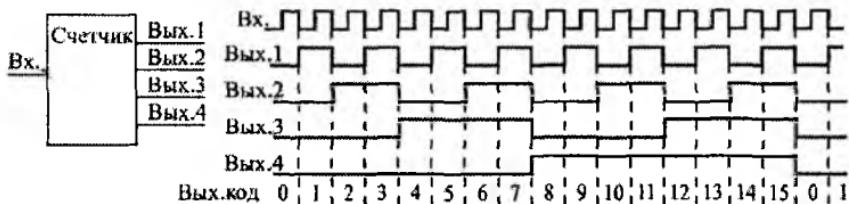

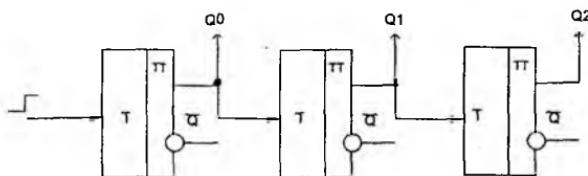

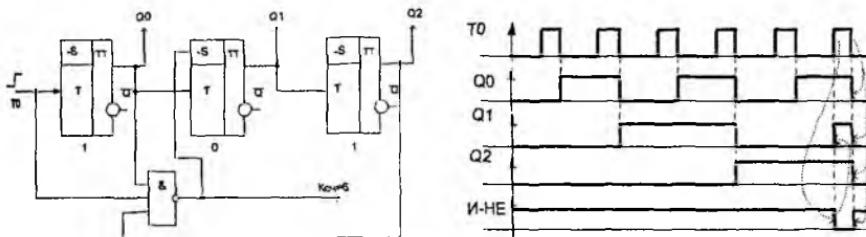

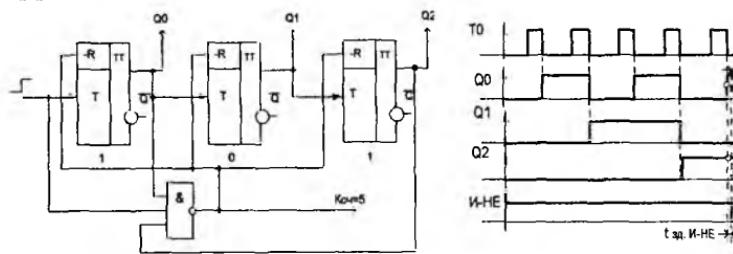

| 8. Счетчики                                                                                                            | 94  |

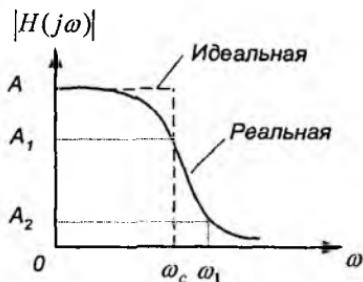

| 9. Исследование работы активных фильтров                                                                               | 115 |

| 10. Кодирующие и декодирующие устройства                                                                               | 152 |

| 11. Одновибраторы и генераторы                                                                                         | 164 |

| Список литературы                                                                                                      | 175 |

| Кириш                                                                                                           | 9   |

|-----------------------------------------------------------------------------------------------------------------|-----|

| 1 Асосий тушунчалар. Ракамли курилмалар, таркиби.                                                               | 10  |

| 2. Ракамли микросхемаларни кулланиш соҳалари                                                                    | 12  |

| 3. Сумматорлар                                                                                                  | 16  |

| 4. Компораторнинг тузилиш схемаси ва иш принципи                                                                | 32  |

| 5. Хотира элементлари - триггерлар, асинхрон ва синхрон RS-триггер. D-триггер, Т-триггер ва универсалJK-триггер | 39  |

| 6. Регистрлар. Регистрларнинг параллельва кетма кет ишилаш принципи                                             | 63  |

| 7. Кодўзгарткичлар                                                                                              | 87  |

| 8. Хисоблагичлар                                                                                                | 94  |

| 9. Актив фильтрларнинг ишини текшириш                                                                           | 115 |

| 10 Кодловчи ва декодерлар                                                                                       | 152 |

| 11. Яккавибраторлар ва генераторлар                                                                             | 164 |

| Адабиетлар руйхати                                                                                              | 175 |

## Content

|                                                                                                                                             |            |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <b>Introduction</b>                                                                                                                         | <b>9</b>   |

| 1. Basic concepts. Digital devices, structure                                                                                               | 10         |

| 2. Applications of digital microcircuits                                                                                                    | 12         |

| 3. Adders                                                                                                                                   | 16         |

| 4. Diagram of the structure and principle of operation of the<br>comparator                                                                 | 32         |

| 5. The storage elements are triggers, asynchronous and syn-<br>chronous RS-triggers. D-flip-flop, T-flip-flop and universal<br>JK-flip-flop | 39         |

| 6. Registers. Parallel and sequential operation of registers                                                                                | 63         |

| 7. Codeconverters.                                                                                                                          | 87         |

| 8. Counters                                                                                                                                 | 94         |

| 9. Research of active filters operation                                                                                                     | 115        |

| 10. Encoders and decoders                                                                                                                   | 152        |

| 11. Single vibrators and generators                                                                                                         | 164        |

| <b>Bibliography</b>                                                                                                                         | <b>175</b> |

## **Введение**

Современный этап развития АСУТП характеризуется применением индустриальных технологий создания и внедрения АСУТП на базе серийно выпускаемых промышленных контроллеров, совместимых с персональными компьютерами и мощных программно-технических комплексов (ПТК) поддержки программирования АСУТП – SCADA систем, а также развития и стандартизации сетевых технологий.

Учитывая изложенное, в настоящее время в Республике Узбекистан уделяется большое внимание подготовке в высших учебных заведениях высококвалифицированных специалистов по автоматизации технологических процессов и управления в водном хозяйстве.

В связи с этим, в настоящее время имеется потребность в подготовке и издании учебного пособия, позволяющего студентам бакалавриата направления 5311000-«Автоматизация и управление технологических процессов и производств (в водном хозяйстве)» в соответствии с учебными планами получить необходимые знания и навыки по применению элементов современных цифровых систем управления при создании АСУТП в сельском и одном хозяйстве.

Целью дисциплины «Цифровое управление» является обучение студентов теоретическим основам, методам и средствам создания цифровых систем управления и формирования у них навыков для самостоятельного решения теоретических и прикладных задач автоматизации технологических процессов на технологических объектах сельского и водного хозяйства.

Учитывая это, в данном учебном пособии отражены теоретические и практические вопросы, знание которых требуется для создания современной цифровых систем управления в сельском и водном хозяйстве.

В настоящее время цифровые устройства выполняются в основном с применением микроконтроллеров, сигнальных процессоров и специализированных микросхем, таких как кодеки, модемы, аналого-цифровые или цифроаналоговые преобразователи. При этом достаточно часто возникают вопросы согласования сигналов, которыми обмениваются данные микросхемы. Иногда требуется инверсия управляющих или информационных сигналов, иногда не совсем совпадают протоколы обмена (вид сигналов записи и чтения, сигналы стробирования данных). В этом случае применение больших интегральных микросхем, таких как ПЛИС CPLD или FPGA нецелесообразно. Это либо невыгодно экономически, либо требуется большая площадь на печатной плате цифрового устройства. В то же самое время применение старых типов микросхем малой интеграции, таких как 1533 или 1564 неприемлемо либо из-за больших габаритов корпуса этих микросхем, либо несовместимости логических уровней, либо недопустимых времен распространения сигнала.

# 1. ОСНОВНЫЕ ПОНЯТИЯ.

## ЦИФРОВЫЕ УСТРОЙСТВА, СТРУКТУРА

**Виды цифровых микросхем.** Вся современная схемотехника разделяется на две большие области: аналоговую и цифровую. Аналоговая схемотехника характеризуется максимальным быстродействием, малым потреблением энергии и малой стабильностью параметров. Цифровая схемотехника обладает прекрасной повторяемостью параметров. Это привело к её развитию в последние годы. В результате в ряде устройств потребление цифровых модулей оказалось сравнимым и даже меньше потребления аналоговых схем, реализующих те же функции. Основные направления развития цифровых микросхем в настоящее время приведены на рисунке 1.1

Рисунок 1.1 Классификация видов цифровых микросхем

Для того, чтобы лучше понимать особенности работы цифровых микросхем в данном курсе мы кратко повторим особенности основных технологий производства цифровых микросхем, применяемых в настоящее время: ТТЛ.

и КМОП. По мере развития цифровых микросхем их быстродействие достигло впечатляющих результатов. Наиболее быстрые из цифровых микросхем обладают скоростью переключения порядка 3...5 нс. (серия микросхем 74ALS), а внутри кристалла микросхемы, где нет больших ёмкостей нагрузки время переключения измеряется пикосекундами. Таким быстродействием обладают программируемые логические схемы и заказные БИС. В этих микросхемах алгоритм решаемой задачи заключён в их принципиальной схеме.

Часто для решаемой задачи не требуется такого быстродействия, каким обладают современные цифровые микросхемы. Однако за быстродействие приходится платить:

1. Быстродействующие микросхемы потребляют значительный ток.

2. Для решения задачи приходится использовать много микросхем, это выливается в стоимость и габариты устройства.

Первую задачу решает применение технологии КМОП цифровых микросхем (например, микросхемы серий 1564, 74HC, 74AHC). Потребляемый ими ток зависит от скорости переключения логических вентилей. Именно поэтому в настоящее время подавляющее большинство микросхем выпускается именно по этой технологии.

Вторую задачу решают несколькими способами. Для жёсткой логики это разработка **специализированных БИС**. Использование специализированных БИС позволяет уменьшить габариты устройства, но стоимость его снижается только при крупносерийном производстве. Для среднего и малого объёмов производства такое решение неприемлемо.

Ещё одним решением уменьшения габаритов и стоимости устройства является применение программируемых логических схем (**ПЛИС**). Это направление активно развивается в настоящее время.

## 2. ОБЛАСТИ ПРИМЕНЕНИЯ ЦИФРОВЫХ МИКРОСХЕМ

**Общие сведения.** Цифровые микросхемы первоначально разрабатывались для построения электронно-вычислительных машин, получивших в дальнейшем название компьютеры. То есть первое их предназначение было заменить человека при выполнении рутинной работы. Сейчас, наверное, никто и не вспомнит, что слово калькулятор ещё каких-нибудь шестьдесят лет назад обозначало не маленький карманный прибор, а профессию большого числа людей, которые занимались расчётами по конкретным математическим формулам. Однако вскоре после начала массового производства цифровых микросхем выяснилось, что они оказались очень удобны для управления какими-либо объектами. При этом управляемая схема может обычно находиться в двух состояниях. Например, схема может быть либо включена, либо выключена, светодиод может либо гореть, либо не гореть, соединение в телефонной станции может быть или не быть, радиостанция может находиться в режиме передачи или в режиме приёма. В результате цифровые микросхемы практически полностью вытеснили применявшиеся ещё с девятнадцатого века для управления приборами электромагнитные реле и перфокарты.

При выполнении задачи управления для описания состояния объекта достаточно двух значений: напряжение высокое или низкое (положительное или отрицательное) ток протекает или не протекает. Это позволило избавиться от многих неприятных моментов аналоговых схем. Например, ошибка при прохождении через схему не увеличивается (в отличие от шумов), а в ряде случаев даже может быть скомпенсирована. Сами цифровые схемы при правильном использовании не вносят ошибок. Эти свойства цифровых микросхем привели к бурному развитию цифровой техники.

Приведённые преимущества привели к тому, что в дальнейшем цифровая техника стала использоваться и для решения других задач. Например, для формирования высокостабильных колебаний для радиотехнических изделий или для использования в качестве эталонных интервалов времени в часах. Здесь тоже нет необходимости формировать различные уровни напряжения генерируемого сигнала. Достаточно только, чтобы частота генерируемого колебания была стабильной. Затем стали разрабатываться методы и теория применения цифровых микросхем для формирования аналоговых сигналов. И здесь тоже основным фактором была возможность заранее прогнозировать уровень шумов. При этом уровень шума зависит только от сложности схемы, и не зависит (ну, или почти не зависит) от количества схем, через которые

проходит сигнал. Это приводит к возможности передавать сигнал на любое расстояние (или производить любое количество копий сигнала).

**Особенности цифровых устройств.** Изучение цифровой техники начнем с самых элементарных вопросов: из каких элементов строятся цифровые схемы и как они устроены? Затем научимся реализовывать на основе этих простейших элементов цифровые устройства любой сложности. Для этого нам потребуется изучить основы алгебры логики и методы запоминания цифровых сигналов. Мы научимся отображать цифровую информацию и вводить ее в цифровые микросхемы.

Прежде всего отметим, что уровни логических сигналов не уменьшаются при распространении по цифровой схеме. Это означает, что цифровые микросхемы принципиально должны обладать усилением. В то же самое время логические уровни на выходе цифрового устройства точно такие же как и на входе, то есть они не возрастают при прохождении через логический элемент. Это обеспечивается тем, что на выходе цифровой микросхемы происходит ограничение сигнала. То есть цифровые микросхемы работают в ключевом режиме: транзистор может быть только открыт или закрыт. В результате на идеальном транзисторе рассеивания энергии не происходит и это означает, что в цифровых микросхемах можно достичь КПД близкого к 100%.

**Виды цифровых микросхем.** В настоящее время используется несколько видов логических элементов:

- диодно-транзисторная логика (ДТЛ)

- транзисторно-транзисторная логика (ТТЛ, TTL)

- логика на основе комплементарных МОП транзисторов (КМОП, CMOS)

- логика на основе сочетания комплементарных МОП и биполярных транзисторов (BiCMOS)

Первоначально получили распространение цифровые микросхемы, построенные на основе ТТЛ технологии. Поэтому до сих пор существует огромное количество микросхем, построенных по этой технологии или совместимые с этими микросхемами по напряжению питания, логическим уровням и цоколевке. Электронные вычислительные машины выполняют арифметические и логические операции, при этом используется два класса переменных: числа и логические переменные.

- Числа несут информацию о количественных характеристиках системы; над ними производятся арифметические действия.

*Логические переменные* определяют состояние системы или принадлежность её к определённому классу состояний (коммутация каналов, управление работой ЭВМ по программе и т. п.).

Логические переменные могут принимать только два значения: *истина* и *ложь*. В устройствах цифровой обработки информации этим двум значениям переменных ставится в соответствие два уровня напряжения: высокий -- (*логическая «1»*) и низкий -- (*логический 0*). Однако в эти значения не вкладывается смысл количества. Элементы, осуществляющие простейшие операции над такими двоичными сигналами, называют логическими. На основе логических элементов разрабатываются устройства, выполняющие и арифметические, и логические операции. В настоящее время логические элементы (ЛЭ) выполняются с помощью различных технологий, которые определяют численные значения основных параметров ЛЭ и, как следствие, качественные показатели цифровых устройств обработки информации, разработанных на их основе. Поэтому в данном пособии схемотехнике и параметрами ЛЭ различных технологий уделено должное внимание.

**Арифметические основы ЭВМ.** В настоящее время в обыденной жизни для кодирования числовой информации используется десятичная система счисления с основанием 10, в которой используется 10 элементов обозначения: числа 0,1,2,...8,9. В первом (младшем) разряде указывается число единиц, во втором – десятков, в третьем – сотен и т. д.; иными словами, в каждом следующем разряде вес разрядного коэффициента увеличивается в 10 раз.

В цифровых устройствах обработки информации используется двоичная система счисления с основанием 2, в которой используется два элемента обозначения: 0 и 1. Веса разрядов слева направо от младших разрядов к старшим увеличиваются в 2 раза, то есть имеют такую последовательность: 8421. В общем виде эта последовательность имеет вид:

$$\dots \cdot 2^5 \cdot 2^4 \cdot 2^3 \cdot 2^2 \cdot 2^1 \cdot 2^0 \cdot 2^{-1} \cdot 2^{-2} \cdot 2^{-3} \dots$$

и используется для перевода двоичного числа в десятичное. Например, двоичное число 101011 эквивалентно десятичному числу 43:

$$2^5 \cdot 1 + 2^4 \cdot 0 + 2^3 \cdot 1 + 2^2 \cdot 0 + 2^1 \cdot 1 + 2^0 \cdot 1 = 43$$

В цифровых устройствах используются специальные термины для обозначения различных по объёму единиц информации: бит, байт, килобайт, мегабайт и т.д. Бит или двоичный разряд определяет значение

одного какого-либо знака в двоичном числе. Например, двоичное число 101 имеет три бита или три разряда. Крайний справа разряд, с наименьшим весом, называется *младшим*, а крайний слева, с наибольшим весом, – *старшим*.

Байт определяет 8-разрядную единицу информации,  $1\text{байт} = 2^3$  бит, например, 10110011 или 01010111 и т. д.,  $1\text{кбайт} = 2^{10}$  байт,  $1\text{Мбайт} = 2^{10}$  кбайт =  $2^{20}$  байт

Для представления многоразрядных чисел в двоичной системе счисления требуется большое число двоичных разрядов. Запись облегчается, если использовать шестнадцатеричную систему счисления.

Основанием *шестнадцатеричной системы* счисления является число  $16 = 2^4$ , в которой используется 16 элементов обозначения: числа от 0 до 9 и буквы A,B,C,D,E,F. Для перевода двоичного числа в шестнадцатеричное достаточно двоичное число разделить на четырёх – битовые группы: целую часть справа налево, дробную – слева направо от запятой. Крайние группы могут быть неполными. Каждая двоичная группа представляется соответствующим шестнадцатеричным символом. Например, двоичное число 0101110000111001 в шестнадцатеричной системе выражается числом 5C39.

Пользователю наиболее удобна десятичная система счисления. Поэтому многие цифровые устройства, работая с двоичными числами, осуществляют приём и выдачу пользователю десятичных чисел. При этом применяется двоично – десятичный код.

*Двоично – десятичный код* образуется заменой каждой десятичной цифры числа четырёхразрядным двоичным представлением этой цифры в двоичном коде. Например, число 15 представляется как 00010101 BCD (BinaryCodedDecimal). При этом в каждом байте располагаются две десятичные цифры. Заметим, что двоично–десятичный код при таком преобразовании не является двоичным числом, эквивалентным десятичному числу.

### 3. СУММАТОРЫ

**Общие сведения.** Сумматор (английское Adder) - логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. Например, если один входной код - 7 (0111), а второй - 5 (0101), то суммарный код на выходе будет 12 (1100). Сумма двух двоичных чисел с числом разрядов  $N$  может иметь число разрядов ( $N + 1$ ). Например, при суммировании чисел 13 (1101) и 6 (0110) получается число 19 (10011). Поэтому количество выходов сумматора на единицу больше количества разрядов входных кодов. Этот дополнительный (старший) разряд называется выходом переноса. При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное.

На схемах сумматоры обозначаются буквами SM. В отечественных сериях код, обозначающий микросхему сумматора, - ИМ.

Сумматоры классифицируют по различным признакам.

В зависимости от системы счисления различают:

- двоичные;

- двоично-десятичные (в общем случае двоично-кодированные);

- десятичные;

- прочие (например, амплитудные).

По количеству одновременно обрабатываемых разрядов складываемых чисел:

- одноразрядные,

- многоразрядные.

По числу входов и выходов одноразрядных двоичных сумматоров:

- четвертьсумматоры (ЛЭ «сумма по модулю 2»; ЛЭ «исключающее ИЛИ»), характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма;

- полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом - перенос в следующий (более старший разряд);

- полные одноразрядные двоичные сумматоры, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды

двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд).

По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на:

- последовательные, в которых обработка чисел ведётся поочерёдно, разряд за разрядом на одном и том же оборудовании;

- параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование.

Параллельный сумматор в простейшем случае представляет собой п одноразрядных сумматоров, последовательно (от младших разрядов к старшим) соединённых цепями переноса. Однако такая схема сумматора характеризуется сравнительно невысоким быстродействием, так как формирование сигналов суммы и переноса в каждом  $i$ -ом разряде производится лишь после того, как поступит сигнал переноса с  $(i-1)$ -го разряда. Таким образом, быстродействие сумматора определяется временем распространения сигнала по цепи переноса. Уменьшение этого времени - основная задача при построении параллельных сумматоров. Для уменьшения времени распространения сигнала переноса применяют: конструктивные решения, когда используют в цепи переноса наиболее быстродействующие элементы; тщательно выполняют монтаж без длинных проводников и паразитных ёмкостных составляющих нагрузки и (наиболее часто) структурные методы ускорения прохождения сигнала переноса.

По способу организации межразрядных переносов параллельные сумматоры, реализующие структурные методы, делят на сумматоры:

- с последовательным переносом;

- с параллельным переносом;

- с групповой структурой;

- со специальной организацией цепей переноса.

Среди сумматоров со специальной организацией цепей переноса можно указать:

- сумматоры со сквозным переносом, в которых между входом и выходом переноса одноразрядного сумматора оказывается наименьшее число логических уровней;

- сумматоры с двухпроводной передачей сигналов переноса;

- сумматоры с условным переносом (вариант сумматора с групповой структурой, позволяющий уменьшить время суммирования в 2 раза при увеличении оборудования в 1,5 раза);

- асинхронные сумматоры, вырабатывающие признак завершения операции суммирования, при этом среднее время суммирования уменьшается, поскольку оно существенно меньше максимального.

Сумматоры, которые имеют постоянное время, отводимое для суммирования, независимое от значений слагаемых, называют синхронными.

**По способу выполнения операции сложения и возможности сохранения результата сложения можно выделить три основных вида сумматоров:**

- комбинационный, выполняющий микрооперацию « $S = A$  плюс  $B$ », в котором результат выдаётся по мере его образования (это комбинационная схема в общепринятом смысле слова);

- сумматор с сохранением результата « $S = A$  плюс  $B$ »;

- накапливающий, выполняющий микрооперацию « $S = S$  плюс».

Последние две структуры строятся либо на счётных триггерах (используются мало), либо по структуре «комбинационный сумматор – регистр хранения» (наиболее употребляемая схема).

**Важнейшими параметрами сумматоров являются:**

- разрядность;

- статические параметры:  $U_{вх}$ ,  $U_{вх}$ ,  $I_{вх}$  и так далее, то есть обычные параметры интегральных схем.

**Сумматоры характеризуются четырьмя задержками распространения:**

- от подачи входного переноса до установления всех выходов суммы при постоянном уровне на всех входах слагаемых;

- от одновременной подачи всех слагаемых до установления всех выходов суммы при постоянном уровне на входе переноса;

- от подачи входного переноса до установления выходного переноса при постоянном уровне на входах слагаемых;

- от подачи всех слагаемых до установления выходного переноса при постоянном уровне на входах слагаемых.

**Параметрами сумматоров являются:**

- разрядность;

- статические параметры:  $U_{bx}$ ,  $U_{vx}$ ,  $I_{bx}$  и т. п. (параметры интегральных микросхем);

- динамические параметры.

Сумматоры характеризуются четырьмя задержками распространения:

- от подачи входного переноса до установления всех выходов суммы при постоянном уровне на всех входах слагаемых;

- от одновременной подачи всех слагаемых до установления всех выходов суммы при постоянном уровне на входе переноса;

- от подачи входного переноса до установления выходного переноса при постоянном уровне на входах слагаемых;

- от подачи всех слагаемых до установления выходного переноса при постоянном уровне на входах слагаемых.

**Четвертьсумматор.** Простейшим двоичным суммирующим элементом является четвертьсумматор. Происхождение названия этого элемента следует из того, что он имеет в два раза меньше выходов и в два раза меньше строк в таблице истинности по сравнению с полным двоичным одноразрядным сумматором. Наиболее известны для данной схемы названия: элемент «сумма по модулю 2» и элемент «исключающее ИЛИ».

Работа схемы описывается как  $S = \bar{a}\bar{b} + a\bar{b} = a \oplus b$ .

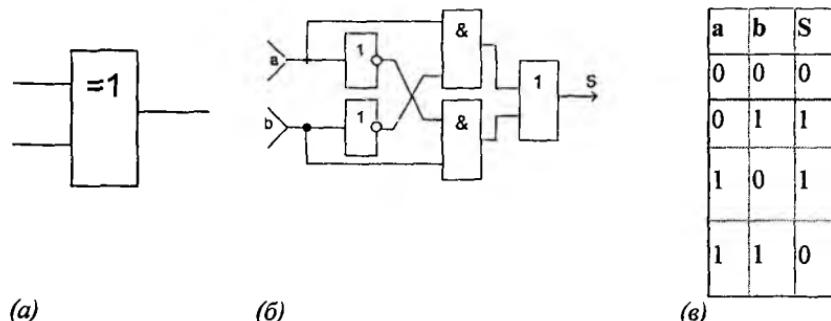

На рис.1 приведено условное обозначение, схема, таблица истинности четвертьсумматора.

Рис.1. Условное обозначение (а), схема (б) и таблица истинности четвертьсумматора.

Четвертьсумматор может быть реализован в базисе И-НЕ или ИЛИ-НЕ.

$$S = \bar{a}\bar{b} + a\bar{b} = \bar{a}a + \bar{a}\bar{b} + \bar{b}b + a\bar{b} = \\ = a(\bar{a} + b) + b(\bar{a} + \bar{b}) = a\bar{a}\bar{b} + b\bar{a}\bar{b} = \underline{\underline{a\bar{a}\bar{b}}} + \underline{\underline{b\bar{a}\bar{b}}} =$$

$$S = \bar{a}\bar{b} + a\bar{b} = \bar{a}a + \bar{a}\bar{b} + \bar{b}b + a\bar{b} = \\ = \underline{\underline{\bar{a}(a+b)}} + \underline{\underline{b(a+b)}} = a + a + b + b + a + b$$

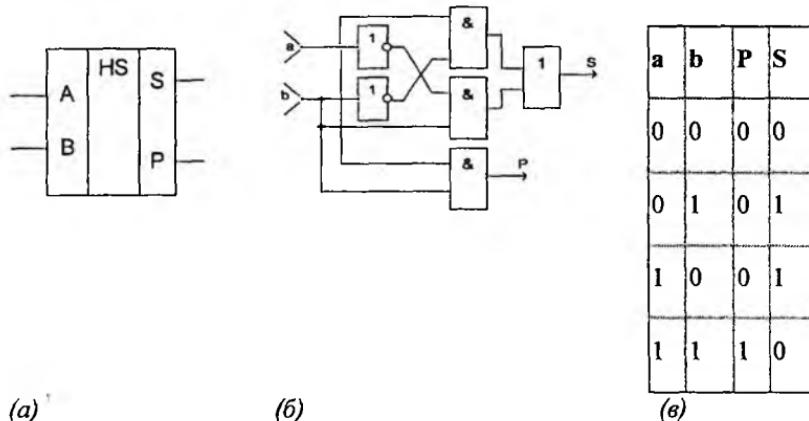

**Полусумматор.** Полусумматор имеет два входа  $a$  и  $b$  для двух слагаемых и два выхода:  $S$  - сумма,  $P$  - перенос.

Обозначением полусумматора служат буквы HS (half sum — полусумма).

Работа полусумматора описывается логическими выражениями для суммы и переноса

$$S = \bar{a}\bar{b} + a\bar{b} = a \oplus b$$

$$P = ab$$

На Рис.2. приведено условное обозначение, схема, таблица истинности полу-сумматора.

(a)

(б)

(в)

Рис.2. Условное обозначение (а), схема (б) и таблица истинности полу-сумматора

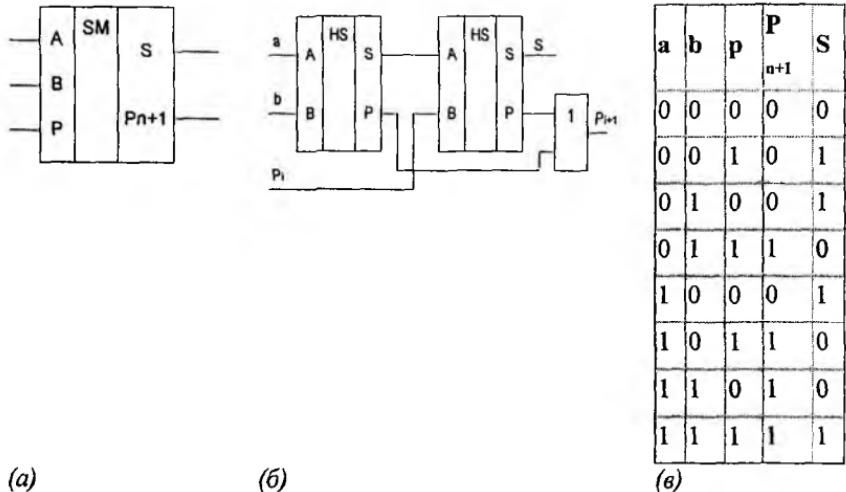

**Полный одноразрядный двоичный сумматор.** Полный одноразрядный сумматор — это устройство для сложения трех одноразрядных двоичных чисел:  $a$ ,  $b$ ,  $P$ .  $P$  — это сигнал переноса из предыдущего младшего разряда.

Полный сумматор имеет два выхода:  $S$  (сумма) и  $P_{n+1}$  (перенос, возникающий в разряде). На Рис.3. приведено условное обозначение, схема, таблица истинности полного сумматора.

Рис.3. Условное обозначение (а), схема (б) и таблица истинности полного сумматора

Выражения, описывающие работу полного двоичного сумматора (согласно таблице истинности), представленные в совершенной дизъюнктивной нормальной форме (СДНФ), имеют вид:

$$\left. \begin{array}{l} S = \bar{a}\bar{b}p + \bar{a}\bar{b}\bar{p} + a\bar{b}p + abp \\ P = \bar{a}bp + a\bar{b}p + ab\bar{p} + abp \end{array} \right\}$$

При практическом проектировании сумматора уравнения S и P могут быть преобразованы к виду, удобному для реализации на заданных логических элементах с некоторыми ограничениями (по числу логических входов и другие) и удовлетворяющему предъявляемым к сумматору требованиям по быстродействию.

Выражение для переноса может быть минимизировано как

$$P = ab + ap + bp$$

Схема полного одноразрядного сумматора может быть построена на логических элементах согласно выражениям S и P или на двух полусумматорах (Рис.3. в).

Полный одноразрядный сумматор (Рис.3.а) имеет три входа: A, B - для двух слагаемых и P - для переноса из предыдущего (более младшего) разряда и два выхода: S - сумма,  $P_{i+1}$  - перенос в следующий (более старший) разряд. Обозначением полного двоичного сумматора служат буквы SM. В таблице истинности (Рис.3.в) выходные сигналы P и S не случайно расположены именно в такой последовательности. Это подчеркивает, что PS рассматрива-

ется как двухразрядное двоичное число, например,  $1 + 1 = 2_{10} = 10_2$ , то есть Р = 1, а S = 0 или  $1 + 1 + 1 = 3_{10} = 11_2$ , то есть Р = 1, а S = 1.

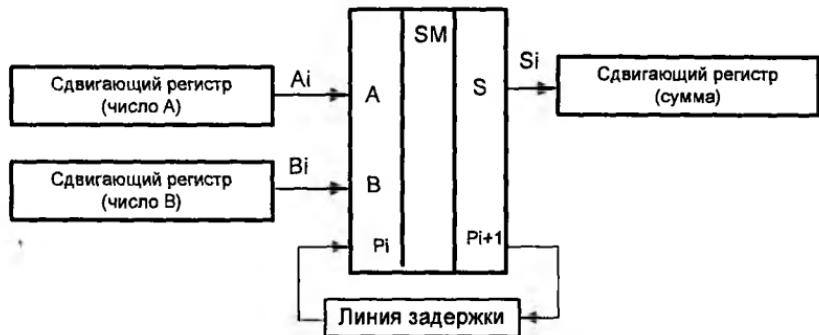

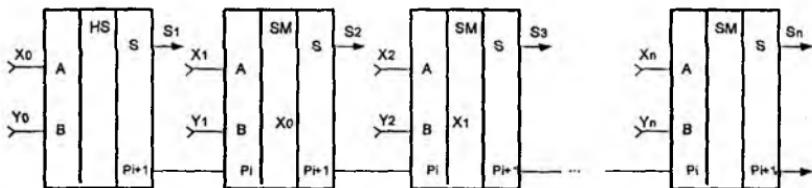

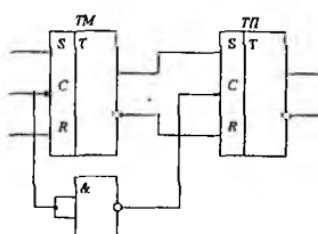

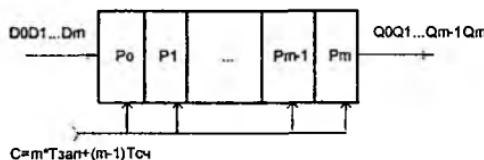

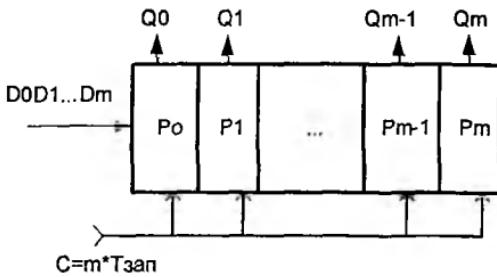

**Многоразрядные сумматоры.** Используя полный сумматор можно построить суммирующее устройство для сложения многоразрядных двоичных чисел А и В. Различают многоразрядные последовательные и параллельные сумматоры. **Последовательный многоразрядный сумматор.** Последовательный многоразрядный сумматор состоит из одноразрядного сумматора на входы а и в которого из сдвигающих регистров, в которых хранятся n-разрядные числа А и В, подаются по тактам разряда за разрядом коды этих чисел, начиная с младшего разряда. Сформированная сумма накапливается в сдвигающем регистре суммы. Возникающий перенос с задержкой на элементе задержки на один такт поступает на вход сумматора только в следующем такте, когда на входы, а и будут поданы следующие разряды чисел А и В.

Схема последовательного сумматора представлена на рис.4. Достоинством последовательного сумматора является простота схемы, требующая минимального количества оборудования, недостатком – низкое быстродействие, т.к. для сложения кодов n-разрядных чисел требуется, учитывая возможность переполнения, n-1 такт работы.

Рис.4. Последовательный многоразрядный сумматор

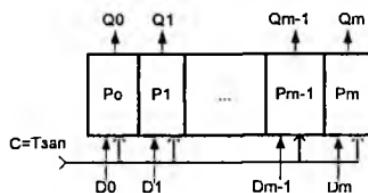

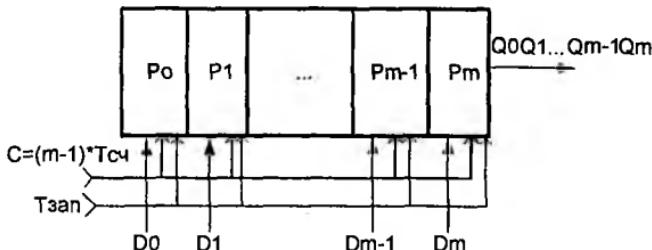

**Параллельный многоразрядный сумматор с последовательным переносом.** В этом сумматоре (Рис5) операция суммирования производится одновременно за один такт во всех разрядах чисел А и В, которые поступают на входы параллельным кодом.

Параллельный многоразрядный сумматор состоит из одного полусумматора (суммирование младших разрядов А и В) и n-1 полных сумматоров, где n – разрядность складываемых чисел.

Рис.5. Параллельный многоразрядный сумматор

Длительность формирования результата в таком сумматоре определяется временем установления выходных сигналов (сумма и перенос) в каждом из одноразрядных сумматоров после установления сигнала на его входах. Надо учитывать, что если на входы  $X_i$  и  $Y_i$  всех разрядов сигналы поступают в момент начала такта, то на вход  $P_i$  сигнал переноса поступает с некоторой задержкой, которая определяется длительностью переходных процессов  $t_{зд}$  в сумматоре предыдущего разряда. При наиболее неблагоприятном сложении, т.е. если, например,  $X = 111\dots 11$ , а  $Y = 000\dots 01$ , произойдет перенос 1 через все сумматоры, т.е. время установления результата будет равно

$$T_{уст.рез.} = t_{зд} * (n-1).$$

При большой разрядности чисел  $T_{уст.рез.}$  может быть большим, следовательно длительность времени подачи чисел  $X, Y$  на входы одноразрядных сумматоров должна быть больше  $T_{уст.рез.}$ . Для ускорения процесса формирования переноса используют дополнительные комбинационные схемы, позволяющие формировать перенос параллельно во всех разрядах.

**Параллельный многоразрядный сумматор с параллельным переносом.** Принцип построения таких сумматоров заключается в том, что значение каждого разряда суммы получается в результате параллельного анализа соответствующих разрядов слагаемых.

Параллельные сумматоры с одновременным переносом бывают двух типов:

- сумматоры с формированием переноса в каждый разряд

- сумматоры без явного формирования переноса

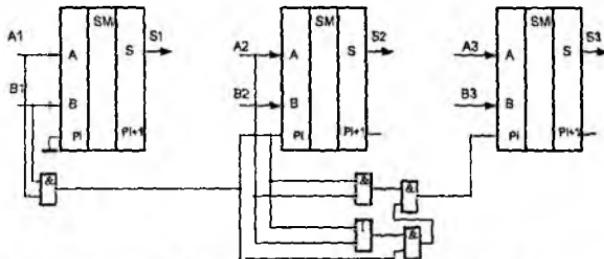

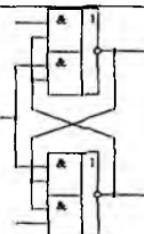

Принцип формирования параллельного переноса показан на Рис. 1.6.

Рис. 6. Принцип формирования параллельного переноса

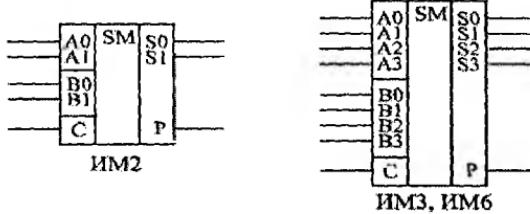

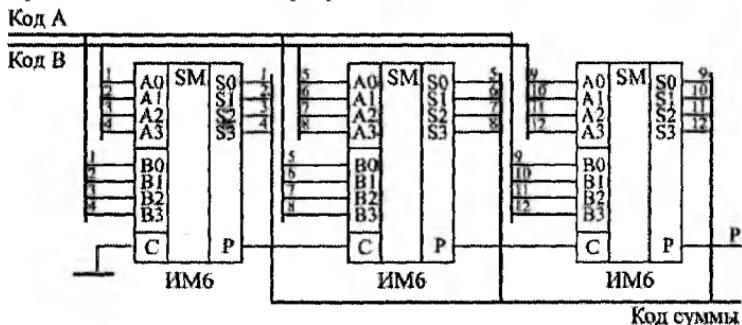

**Микросхемы многоразрядных сумматоров.** На рис. 7 показаны для примера 2-разрядный и 4-разрядный сумматоры.

Микросхема ИМ6 отличается от ИМ3 повышенным быстродействием и номерами используемых выводов микросхемы, функция же выполняется та же самая. Помимо выходных разрядов суммы и выхода переноса, сумматоры имеют вход расширения (другое название - вход переноса) С для объединения нескольких сумматоров с целью увеличения разрядности. Если на этот вход приходит единица, то выходная сумма увеличивается на единицу, если же приходит нуль, то выходная сумма не увеличивается.

Если используется одна микросхема сумматора, то на ее вход расширения С необходимо подать нуль.

Рис. 7. Примеры микросхем сумматоров

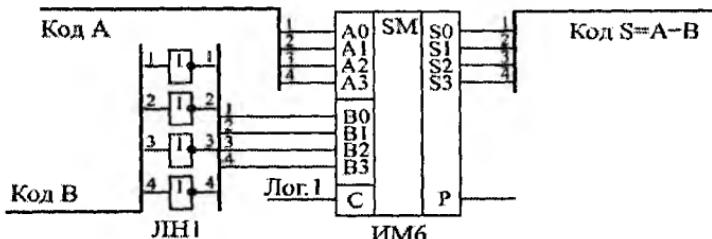

Сумматор может вычислять не только сумму, но и разность входных кодов, то есть работать вычитателем. Для этого вычитаемое число надо просто поразрядно проинвертировать, а на вход переноса С подать единичный сигнал (Рис. 8).

Рис. 8. 4-х разрядный вычитатель на сумматоре ИМ6 и инверторах ЛН1

Например, пусть нам надо вычислить разность между числом 11 (1011) и числом 5 (0101). Инвертируем поразрядно число 5 и получаем 1010, то есть десятичное 10. Сумматор при суммировании 11 и 10 даст 21, то есть двоичное число 10101. Если сигнал С равен 1, то результат будет 10110. Отбрасываем старший разряд (выходной сигнал Р) и получаем разность 0110, то есть 6. Каскадировать сумматоры для увеличения разрядности очень просто. Надо сигнал с выхода переноса сумматора, обрабатывающего младшие разряды, подать на вход переноса сумматора, обрабатывающего старшие разряды (Рис. 9). При объединении трех 4-разрядных сумматоров получается 12-разрядный сумматор, имеющий дополнительный 13-й разряд (выход переноса Р). Неопределенные состояния на выходах сумматора могут возникать при любом изменении любого из входных кодов (Рис. 10).

Выходной код суммы может принимать в течение короткого времени значения, никак не связанные с входными кодами, а на выходе переноса могут появляться короткие паразитные импульсы. Это связано, прежде всего, с неодновременным изменением разрядов входных кодов.

Рис. 9. Каскадирование сумматоров ИМ6 для увеличения разрядности

Чтобы избежать влияния этих неопределенных состояний на дальнейшую схему, необходимо предусматривать синхронизацию или стробирование

выходных сигналов. Для этого надо располагать информацией о моментах изменения входных кодов.

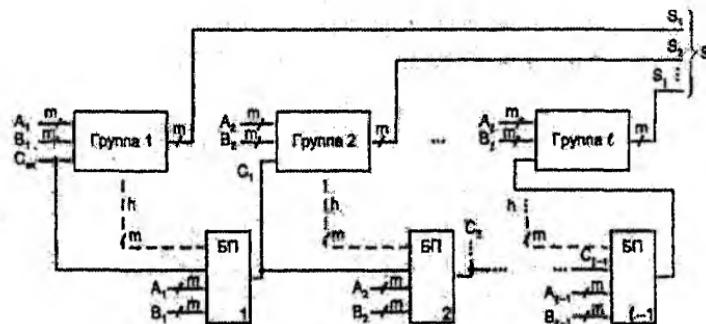

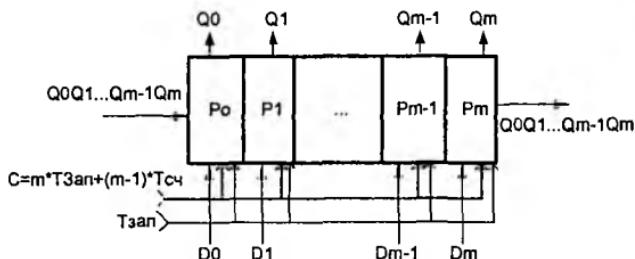

**Сумматоры групповой структуры.** В сумматорах групповой структуры схема с разрядностью  $n$  делится на  $l$  групп по  $m$  разрядов ( $n=lm$ ). В группах и между ними возможны различные виды переносов, что порождает множество вариантов групповых сумматоров.

Существуют групповые сумматоры с цепным (последовательным) и параллельным переносами между группами. В самих группах перенос при этом может быть любым. Групповой сумматор с цепным переносом при  $l$  группах имеет  $l-1$  блок переноса. Блоки переноса включены последовательно и образуют тракт передачи переноса (Рис.10.). Слагаемые разбиты на  $m$ -разрядные поля, суммируемые в группах. Результат также составляется из  $m$ -разрядных полей. Блоки переноса  $БП_i$ , ( $i=1\dots l-1$ ) анализируют слагаемые в пределах группы, и если из группы должен быть перенос, то он появляется на выходе блока для подачи на вход следующей группы и в цепочку распространения переноса от младших групп к старшим. Максимальная длительность суммирования для варианта с цепным переносом

$$t_{sm} = (l-1) t_{bp} + t_{rp}.$$

Рис. 10. Групповой сумматор с цепным переносом между группами

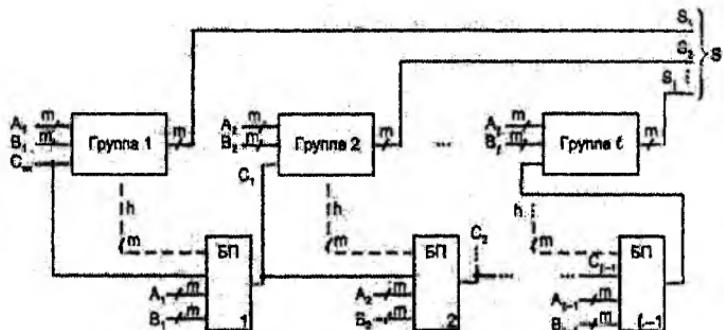

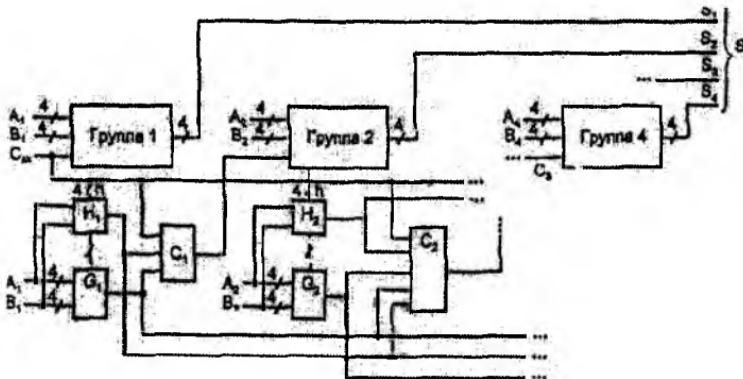

Сумматор с параллельными межгрупповыми переносами строится по структуре, сходной со структурой сумматора с параллельным переносом, в которой роль одноразрядных сумматоров играют группы. Структура группового сумматора с параллельными межгрупповыми переносами показана на Рис. 11, где разрядность и число групп приняты равными 4. Время суммирования для такой схемы составляет  $T_{sm} = t_h + t_G + t_C + t_{rp}$ .

выходных сигналов. Для этого надо располагать информацией о моментах изменения входных кодов.

**Сумматоры групповой структуры.** В сумматорах групповой структуры схема с разрядностью  $n$  делится на  $l$  групп по  $m$  разрядов ( $n=lm$ ). В группах и между ними возможны различные виды переносов, что порождает множество вариантов групповых сумматоров.

Существуют групповые сумматоры с цепным (последовательным) и параллельным переносами между группами. В самих группах перенос при этом может быть любым. Групповой сумматор с цепным переносом при  $l$  группах имеет  $l-1$  блок переноса. Блоки переноса включены последовательно и образуют тракт передачи переноса (Рис.10.). Слагаемые разбиты на  $m$ -разрядные поля, суммируемые в группах. Результат также составляется из  $m$ -разрядных полей. Блоки переноса  $BP_i$ , ( $i=1\dots l-1$ ) анализируют слагаемые в пределах группы, и если из группы должен быть перенос, то он появляется на выходе блока для подачи на вход следующей группы и в цепочку распространения переноса от младших групп к старшим. Максимальная длительность суммирования для варианта с цепным переносом

$$t_{SM} = (l-1) t_{BP} + t_{rp}.$$

Рис. 10. Групповой сумматор с цепным переносом между группами

Сумматор с параллельными межгрупповыми переносами строится по структуре, сходной со структурой сумматора с параллельным переносом, в которой роль одноразрядных сумматоров играют группы. Структура группового сумматора с параллельными межгрупповыми переносами показана на Рис. 11, где разрядность и число групп приняты равными 4. Время суммирования для такой схемы составляет  $T_{SM} = t_b + t_g + t_c + t_{rp}$ .

Рис. 11. Групповой сумматор с параллельным переносом между группами

К суммирующим схемам относятся сумматоры и схемы вычитания.

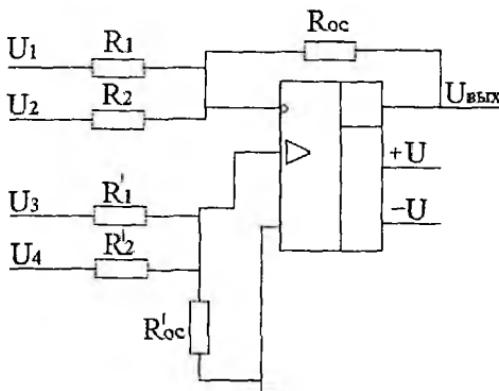

Инвертирующий сумматор формирует алгебраическую сумму двух напряжений и меняет ее знак на обратный. В схеме входные сопротивление имеют ту же величину, что и сопротивление обратной связи.

$$U_{\text{вых}} = U_3 \left( \frac{R_{oc}}{R_1} \right) + U_4 \left( \frac{R_{oc}}{R_2} \right) - U_1 \left( \frac{R_{oc}}{R_1} \right) - U_2 \left( \frac{R_{oc}}{R_2} \right), \text{ если}$$

$$\frac{R_{oc}}{R_1} + \frac{R_{oc}}{R_2} = \frac{R'_1}{R_1} + \frac{R'_2}{R_2}$$

$$\frac{R_{oc}}{R_1} + \frac{R_{oc}}{R_2} + \dots + \frac{R_{oc}}{R_m} = \frac{R'_1}{R_1} + \frac{R'_2}{R_2} + \frac{R'_3}{R_3} + \dots + \frac{R'_n}{R_n}$$

$$U_{\text{вых}} = - \left( U_1 \frac{R_{oc}}{R_1} + U_2 \frac{R_{oc}}{R_2} + \dots + U_m \frac{R_{oc}}{R_m} \right) + \left[ U_{m+1} \frac{R'_1}{R'_1} + U_{m+2} \frac{R'_2}{R'_2} + \dots + U_{m+n} \frac{R'_n}{R'_n} \right]$$

**Пример №1.** Пусть в схеме на рис.12. Дано:  $U_1 = U_2 = 1B$ ,  $U_3 = U_4 = 2B$ ,  $R_{oc} = 200\text{k}\Omega$ ,  $R'_1 = 100\text{k}\Omega$ ,  $R_1 = 100\text{k}\Omega$ ,  $R_2 = R_3 = 25\text{k}\Omega$  и  $R_4 = 16,67\text{k}\Omega$ .

Задание: (а) выполняется ли условие баланса?

(б) Чему равно  $U_{\text{вых}}$ ?

Рис.12

**Решение:**

$$(a) \text{ проверим баланс: } \frac{R_{oc}}{R_1} + \frac{R_{oc}}{R_2} = \frac{R'_{oc}}{R'_1} + \frac{R'_{oc}}{R'_2}$$

$$\frac{200\text{кОм}}{100\text{кОм}} + \frac{200\text{кОм}}{25\text{кОм}} = \frac{100\text{кОм}}{25\text{кОм}} + \frac{100\text{кОм}}{16,67\text{кОм}}$$

$$2+8=10; 4+6=10$$

Таким образом, баланс имеет место.

(б)

$$U_{\text{вых}} = U_3 \frac{R'_{oc}}{R'_1} + U_4 \frac{R'_{oc}}{R'_2} - U_1 \frac{R_{oc}}{R_1} - U_1 \frac{R_{oc}}{R_2}$$

$$U_{\text{вых}} = 2 * \frac{100\text{кОм}}{25\text{кОм}} + 2 * \frac{100\text{кОм}}{16,67\text{кОм}} - 1 * \frac{200\text{кОм}}{100\text{кОм}} - 1 * \frac{200\text{кОм}}{25\text{кОм}}$$

$$= 2 * 4 + 2 * 6 - 1 * 2 - 1 * 8 = 10\text{В}$$

Поэтому  $U_{\text{вых}} = 10\text{В}$

**Задание для самостоятельной работы:**

| № варианта | $U_1 = U_2$<br>B | $U_3 = U_4$<br>B | $R_{oc}$<br>кОм | $R'_{oc}$<br>кОм | $R_1$<br>кОм | $R_2$<br>кОм | $R_3$<br>кОм | $R_4$<br>кОм |

|------------|------------------|------------------|-----------------|------------------|--------------|--------------|--------------|--------------|

| 1          | 2                | 3                | 200             | 100              | 100          | 20           | 20           | 15           |

| 2          | 3                | 5                | 400             | 200              | 200          | 25           | 25           | 23           |

| 3          | 1                | 3                | 300             | 200              | 200          | 35           | 35           | 23           |

| 4          | 1                | 2                | 100             | 50               | 50           | 25           | 25           | 13           |

| 5          | 3                | 4                | 200             | 100              | 100          | 40           | 40           | 25           |

| 6          | 2                | 3                | 400             | 300              | 300          | 45           | 45           | 23           |

| 7          | 4                | 5                | 300             | 200              | 200          | 30           | 30           | 14           |

| 8          | 2                | 3                | 500             | 400              | 400          | 15           | 15           | 12           |

| № варианта | $U_1 = U_2$<br>В | $U_3 = U_4$<br>В | $R_{oc}$<br>кОм | $R'_{oc}$<br>кОм | $R_1$<br>кОм | $R_2$<br>кОм | $R_3$<br>кОм | $R_4$<br>кОм |

|------------|------------------|------------------|-----------------|------------------|--------------|--------------|--------------|--------------|

| 9          | 1                | 2                | 500             | 400              | 400          | 20           | 20           | 12           |

| 10         | 2                | 3                | 300             | 100              | 100          | 30           | 30           | 14           |

| 11         | 3                | 4                | 200             | 100              | 100          | 50           | 50           | 34           |

| 12         | 4                | 5                | 300             | 200              | 200          | 35           | 35           | 16           |

| 13         | 3                | 4                | 500             | 300              | 300          | 45           | 45           | 34           |

| 14         | 2                | 3                | 500             | 400              | 400          | 35           | 35           | 16           |

| 15         | 1                | 2                | 300             | 100              | 100          | 25           | 25           | 12           |

| 16         | 2                | 3                | 200             | 100              | 100          | 15           | 15           | 12           |

| 17         | 3                | 4                | 300             | 200              | 200          | 45           | 45           | 34           |

| 18         | 2                | 3                | 400             | 300              | 300          | 50           | 50           | 26           |

| 19         | 2                | 4                | 300             | 200              | 200          | 35           | 35           | 23           |

| 20         | 3                | 4                | 200             | 100              | 100          | 40           | 40           | 29           |

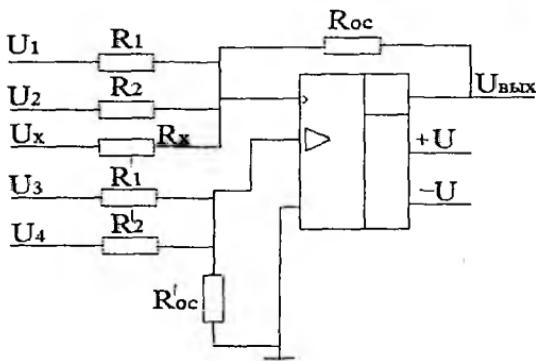

**Пример №2.** Дано: Построить схему сложения-вычитания так, чтобы напряжение на ее выходе было равно:  $U_{\text{вых}} = -4U_1 - 2U_2 + 10U_3 + U_4$

Рис.13

**Решение:** Целесообразно положить  $R_{oc} = R'_{oc}$  поэтому выберем  $R_{oc} = R'_{oc} = 100 \text{ кОм}$ . Для нахождения  $R_1, R_2, R'_1$  и  $R'_2$  можно использовать Соотношение в форме, приведенной на рис 13. так как данная схема имеет всего четыре входа.

Коэффициент при  $U_1$  равен  $\frac{R_{oc}}{R_1} = 4$ , по этому

$$R_1 = \frac{R_{oc}}{4} = \frac{100 \text{ кОм}}{4} = 25 \text{ кОм}$$

Аналогично,

$$\frac{R_{oc}}{R_2} = 2; R_2 = \frac{100\text{k}\Omega}{2} = 50\text{k}\Omega; R'_1 = \frac{R'_{oc}}{10} = 10\text{k}\Omega$$

$$R'_1 = \frac{R'_{oc}}{10} = 10\text{k}\Omega$$

Проверяя наличие баланса видим, что

$$\frac{R_{oc}}{R_1} + \frac{R_{oc}}{R_2} = 4 + 2 = 6$$

и

$$\frac{R'_1}{R'_2} + \frac{R'_{oc}}{R'_2} = 10 + 1 = 11,$$

сумма неинвертирующих коэффициентов усиления на пять больше суммы инвертирующих коэффициентов.

Если изменить схему таким образом, чтобы напряжение на ее выходе стало равным

$$U_{\text{вых}} = -(4U_1 + 2U_2 + 5U_x) + (10U_3 + U_4)$$

И задать  $U_x = 0$ , то полученное выходное напряжение окажется равным желаемому. Нам остается подключить к инвертирующему входу, как показано на рис. 13., такое сопротивление  $R_x$  чтобы отношение  $\frac{R_{oc}}{R_x}$

Было равно 5, и тогда баланс схемы будет обеспечен. Величина  $R_x$  равна

$$\frac{R'_{oc}}{5} = 20\text{k}\Omega$$

Задание для самостоятельной работы:

| № варианта | $R_{oc} = R'_{oc}$ | № варианта | $R_{oc} = R'_{oc}$ |

|------------|--------------------|------------|--------------------|

| 1          | 300                | 11         | 400                |

| 2          | 200                | 12         | 300                |

| 3          | 300                | 13         | 500                |

| 4          | 500                | 14         | 600                |

| 5          | 300                | 15         | 200                |

| 6          | 400                | 16         | 300                |

| 7          | 200                | 17         | 500                |

| 8          | 600                | 18         | 400                |

| 9          | 200                | 19         | 300                |

| 10         | 300                | 20         | 200                |

## **Индивидуальные задания**

**Задание 1.** Нарисуйте схему вычитателя чисел на 16 разрядов на базе микросхемы ИМ2.

**Задание 2.** Нарисуйте схему сумматора двух чисел на 16 разрядов на базе микросхемы ИМ6.

## **Контрольные вопросы**

1. Что такое сумматор.

2. Как классифицируются сумматоры в зависимости от системы счисления?

3. Как классифицируются сумматоры по количеству одновременно обрабатываемых разрядов складываемых чисел?

4. Как классифицируются сумматоры по числу входов и выходов одноразрядных двоичных сумматоров?

5. Как классифицируются сумматоры по способу организации переносов?

6. Назовите параметры сумматоров.

7. Какой сумматор называется четвертьсумматором? Поясните его работу с помощью таблицы истинности и схемы.

8. Какой сумматор называется полусумматором? Поясните его работу с помощью таблицы истинности и схемы.

9. Какой сумматор называется полным сумматором? Поясните его работу с помощью таблицы истинности и схемы.

10. Нарисуйте условные обозначения полусумматора и полного сумматора.

11. Поясните работу последовательного сумматора.

12. Поясните работу параллельного сумматора.

## 4. СХЕМА СТРОЕНИЯ И ПРИНЦИП РАБОТЫ КОМПАРАТОРА

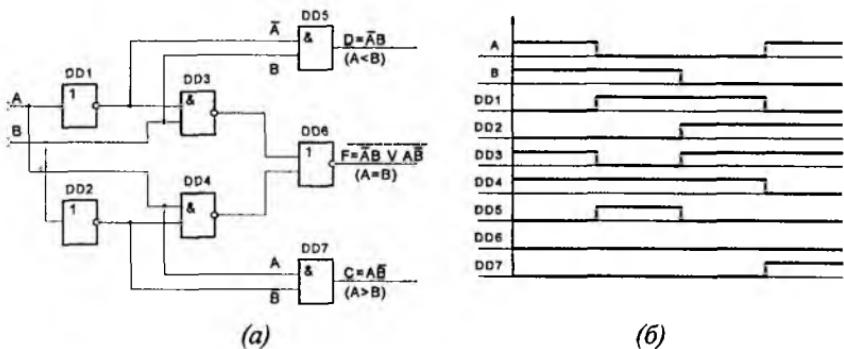

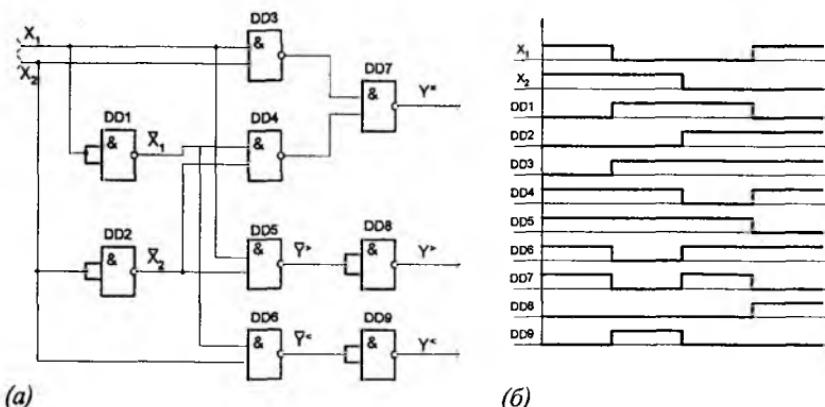

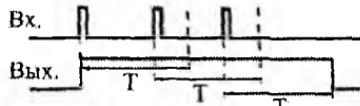

**Общие сведения.** Цифровые компараторы относятся к арифметическим устройствам. Цифровые компараторы (от англ. compare — сравнивать, сличать) выполняют сравнение двух чисел, заданных в двоичном (двоично-десятичном) коде. В зависимости от схемного исполнения компараторы могут определять равенство  $A=B$  ( $A$  и  $B$  - независимые числа с равным количеством разрядов) либо вид неравенства:  $A < B$  или  $A > B$ . Результат сравнения отображается соответствующим логическим уровнем на выходе. Микросхемы - цифровые компараторы - выполняют, как правило, все эти операции и имеют три выхода ( $>$ ,  $<$ ,  $=$ ). Цифровые компараторы широко применяются для выявления нужного числа (слова) в потоке цифровой информации, для отметки времени в часовых приборах, для выполнения условных переходов в вычислительных устройствах. Одноразрядный компаратор. Логическая схема, выполняющая операцию «эквивалентность»  $F=AB \vee \overline{A}\overline{B}$ , или, что то же самое, «исключающее ИЛИ—НЕ», может быть использована как одноразрядный компаратор. Поскольку в практических условиях исключающее ИЛИ применяется чаще, чем эквивалентность, последующее описание будет идти применительно к этой операции. Схема одноразрядного компаратора и диаграмма его работы показаны на рис. 14.

Рис.14. Схема одноразрядного компаратора (а), диаграмма его работы (б)

Она представляет собой развернутую логическую структуру логического элемента «исключающее ИЛИ- НЕ» с тремя выходами. Из определения операции «исключающее ИЛИ» вытекает, что

$$\bar{F} = \overline{A \cdot \overline{B}} \vee \overline{A}\overline{B} = \begin{cases} 1.. при.. A = B \\ 0.. при.. A \neq B \end{cases}$$

При  $A > B$  (это означает, что  $A = 1$ ,  $B = 0$ ) -  $C = AB = 1$ .

При  $A < B$  (это означает, что  $A=0, B=1$ ) -  $D = \overline{AB} = 1$ .

Логические элементы И с выходами С и D приведены для наглядности.

В принципе сигналы С и D можно снимать с выходов внутренних схем И логического элемента И-ИЛИ-НЕ.

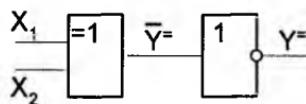

Компаратор на равенство одноразрядных чисел можно выполнить на ЛЭ "исключающее ИЛИ" и инверторе (Рис.2.2.).

Рис. 15. Одноразрядный компаратор на ЛЭ

«исключающий ИЛИ» и инверторе

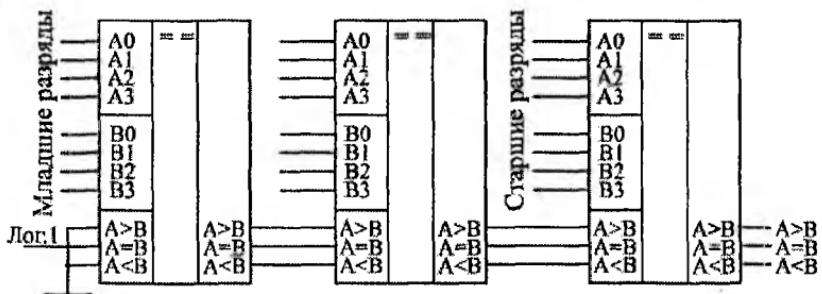

**Многоразрядный компаратор.** Многоразрядные компараторы обычно выполняют на базе одноразрядных с подключением дополнительных ЛЭ И и ИЛИ (для блокировки одноразрядных компараторов и объединения сигналов).

При этом используется принцип последовательного сравнения разрядов многоразрядных чисел, начиная с их старших разрядов, так как уже на этом этапе, если  $X_{1m} \neq X_{2m}$ , задача может быть решена однозначно, и сравнение следующих за старшими разрядов не потребуется.

На практике широко применяются "неполные" компараторы в которых реализуется одна или две операции на сравнение кодов ( $Y =$ ,  $Y >$ ,  $Y = i$  и  $Y > i$  и др.). Для выполнения этих операций можно использовать отдельные фрагменты из схем на Рис.16, или построить специальные схемы, которые в ряде случаев могут быть упрощены.

Рис.16. Схема компаратора на ЛЭ 2И-НЕ (а), диаграмма его работы (б)

На схемах компараторы кодов обозначаются двумя символами равенства: "==".

Код типа микросхемы компаратора кода в отечественных сериях — СП.

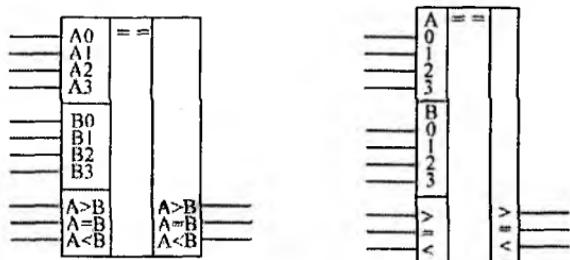

Примером такой микросхемы может служить СП1 - 4-х разрядный компаратор кодов, сравнивающий величины кодов и выдающий информацию о том, какой код больше, или о равенстве кодов (рис.17).

Помимо восьми входов для сравниваемых кодов (два 4-х разрядных кода, обозначаемых A0...A3 и B0...B3), компаратор СП1 имеет три управляющих входа для наращивания разрядности ( $A > B$ ,  $A < B$ ,  $A = B$ ) и три выхода результирующих сигналов ( $A > B$ ,  $A < B$ ,  $A = B$ ).

Для удобства на схемах управляющие входы и выходы иногда обозначают просто ">", "<" и "==".

Нулевые разряды кодов (A0 и B0) -младшие, третий разряды (A3 и B3 - старшие.

Рис. 17. 4-х разрядный компаратор кодов СП1 (два варианта обозначения)

Рис. 18. Каскадирование компараторов кодов

Если микросхемы компараторов кодов каскадируются (объединяются) для увеличения числа разрядов сравниваемых кодов, то надо выходные сиг-

налы микросхемы, обрабатывающей младшие разряды кода, подать на однотипные входы микросхемы, обрабатывающей старшие разряды кода (рис. 18).

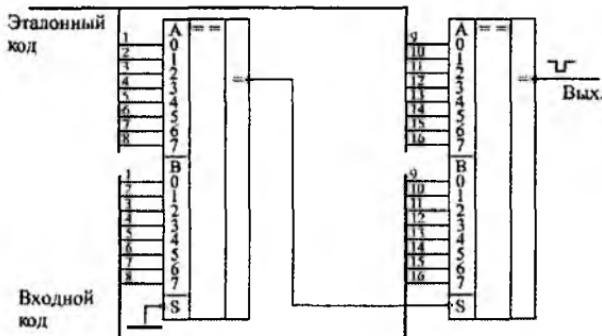

Дно из основных применений компараторов кодов состоит в селектировании входных кодов.

На рис. 19 показано применение компараторов SN74ALS521 для селектирования 16-разрядных кодов. Инверсный сигнал с выхода первой микросхемы подается на инверсный вход разрешения второй микросхемы, выходной сигнал которой (отрицательный) говорит о совпадении входного и эталонного 16-разрядных кодов.

Рис19. Селектирование 16-разрядных кодов

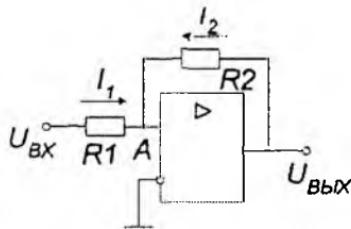

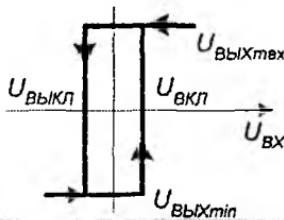

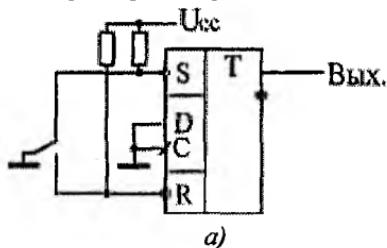

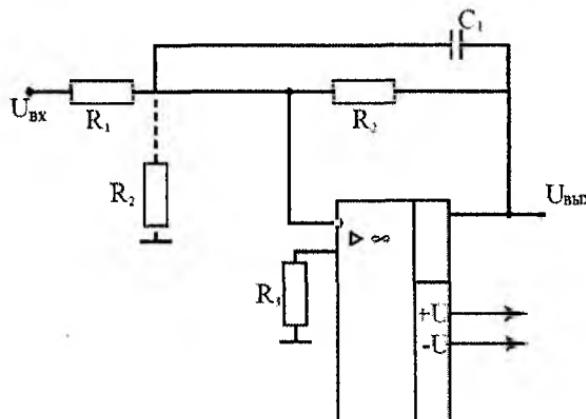

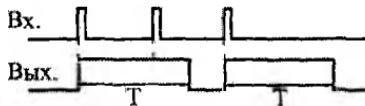

**Пример №1.** Пороговое устройство, изменяющее своё состояние в зависимости от уровней сигналов на его входах называется компаратором. Компаратор осуществляет переключение уровня выходного напряжения. Когда непрерывно изменяющийся во времени сигнал становится ниже или выше определённого уровня. Применим схему триггера Шмидта. В данном схеме напряжение включения выбрано  $-0,2V$ , а напряжение включения  $+0,2V$ . Это связано с тем, что падение напряжения на диоде, включенном параллельно конденсатору в прямом направлении составляет  $+0,6V$ , а уровень напряжения переключения должен находиться около  $0V$ , но не ноль. Для этого устройства используем микросхему КР140УД8, имеющую выход согласованный с ТТЛ логикой.

Определяем величины сопротивлений  $R1$  и  $R2$ :

$$U_{\text{выкл}} = -\frac{R1}{R2} = U_{\text{вых max}}; U_{\text{вкл}} = -\frac{R1}{R2} U_{\text{вых min}}$$

Пусть сопротивление  $R2=15 \text{ к}\Omega$ , тогда из формулы находим:

$$R1 = -\frac{R2 \cdot U_{выхл}}{U_{вых max}} = -\frac{-0,2 \cdot 15000}{5} = 600 \text{ Ом}$$

Аналогичная величина получается, если находить по напряжению включения:

$$R1 = -\frac{R2 \cdot U_{выхл}}{U_{вых min}} = -\frac{0,2 \cdot 15000}{-5} = 600 \text{ Ом}$$

По ГОСТ выбираем 620 Ом.

Для устойчивой работы триггера необходимо выполнить условие:

$$\frac{R1}{R2} \leq 0,9; \frac{600}{15000} = 0,04 \leq 0,9$$

Условие выполняется.

Рис..20 Схема компаратора.

Рис.21 Временная работа компаратора.

### Задание для самостоятельной работы 1:

| № варианта | $U_{вкл}=U_{выхл}$<br>В | R2<br>кОм | № варианта | $U_{вкл}=U_{выхл}$<br>В | R2<br>кОм |

|------------|-------------------------|-----------|------------|-------------------------|-----------|

| 1          | 2                       | 35        | 11         | 0,4                     | 20        |

| 2          | 1                       | 25        | 12         | 0,2                     | 25        |

| 3          | 3                       | 50        | 13         | 2                       | 15        |

| 4          | 0,2                     | 45        | 14         | 1                       | 26        |

| 5          | 0,4                     | 40        | 15         | 0,5                     | 35        |

| 6          | 1                       | 30        | 16         | 3                       | 50        |

| 7          | 0,5                     | 20        | 17         | 0,1                     | 35        |

| 8          | 3                       | 15        | 18         | 0,3                     | 14        |

| 9          | 0,3                     | 25        | 19         | 2                       | 19        |

| 10         | 1                       | 15        | 20         | 1                       | 35        |

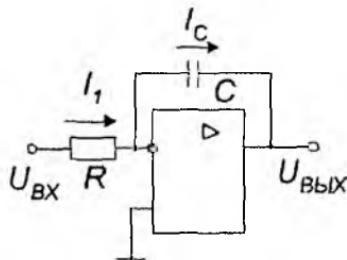

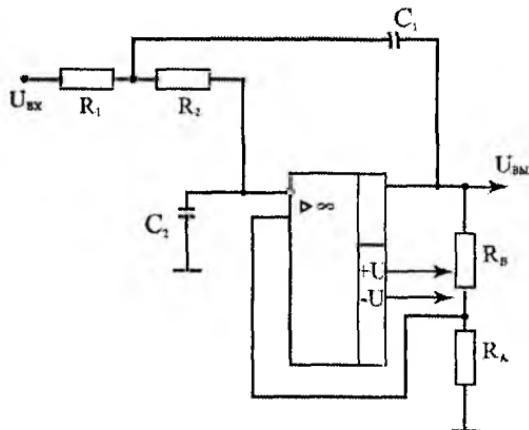

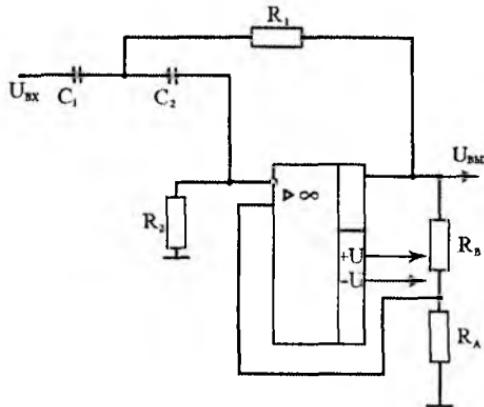

Пример №2. Интегратор - это устройство представляющее собой операционный усилитель, обратная положительная связь которого образован

элементом с интегро-дифференциальной связью между током и напряжением. Таким элементом в данном случае является ёмкость. ОУ включен как генератор стабильного тока в цепь заряда конденсатора. В результате этого заря конденсатора происходит не по экспоненциальному, а по линейной функции зависимости напряжения от времени. Схема действует как накопитель, в котором суммируется входной сигнал за заданный отрезок времени. Из условий задания определяем:

$$M = \frac{U_{bx} 2^n}{U_{op}} = \frac{5 \cdot 2^8}{15} = 85,333$$

$$t = \frac{M}{f_i} = \frac{85,333}{50000} = 1,707 \mu s$$

$$T = \frac{2^n}{f_i} = \frac{256}{50000} = 5,12 \mu s$$

$$U_{bx} = -\frac{U_{bx}}{RC} T$$

$R=47$  кОм и в начале в течении  $1,707$  мS интегрируется входное напряжение  $+5V$ , а также напряжение на выходе спадает до  $-E=-15V$ , то

$$C = -\frac{U_{bx}}{U_{bx} R} T = -\frac{5}{47000 \cdot 15} \times 5,12 \cdot 10^{-3} = 36 \text{ нФ}$$

По ГОСТ выбираем 36 нФ.

Аналогично для второго интервала эта же ёмкость будет иметь такое же значение. И выполняется равенство

$$\frac{U_{bx}}{RC} T = \frac{U_{bx}}{RC} t; \quad \frac{5 \cdot 5,12 \cdot 10^{-3}}{47000 \cdot 36 \cdot 10^{-9}} = \frac{1,707 \cdot 10^{-3}}{47000 \cdot 36 \cdot 10^{-9}} = 15$$

Ток заряда конденсатора при этом составляет

$$I = \frac{U}{R_i} = \frac{15}{47000} = 319 \mu A$$

Параллельно конденсатору включён диод типа Д220 для того, чтобы интегрирование входного напряжения начиналось с  $+0,6V$ .

Рис.22. Схема интегратора

**Задание для самостоятельной работы 2:**

| № варианта | U <sub>вх</sub> (В) | U <sub>вых</sub> (В) | R (кОм) |

|------------|---------------------|----------------------|---------|

| 1          | 9                   | 12                   | 15      |

| 2          | 1,5                 | 3                    | 23      |

| 3          | 3                   | 5                    | 16      |

| 4          | 5                   | 9                    | 34      |

| 5          | 12                  | 24                   | 45      |

| 6          | 24                  | 36                   | 34      |

| 7          | 9                   | 12                   | 20      |

| 8          | 1,5                 | 3                    | 15      |

| 9          | 3                   | 5                    | 23      |

| 10         | 5                   | 9                    | 56      |

| 11         | 12                  | 24                   | 37      |

| 12         | 24                  | 36                   | 57      |

| 13         | 9                   | 12                   | 23      |

| 14         | 9                   | 12                   | 17      |

| 15         | 1,5                 | 3                    | 34      |

| 16         | 3                   | 5                    | 56      |

| 17         | 5                   | 9                    | 23      |

| 18         | 12                  | 24                   | 46      |

| 19         | 24                  | 36                   | 45      |

| 20         | 9                   | 12                   | 25      |

**Индивидуальные задания**

Задание 1. Используя микросхему СП1 нарисуйте схему определения максимального из двух 16-ти разрядных чисел.

**Контрольные вопросы**

1. Что такое компаратор?

2. Объясните работу схемы одноразрядного компаратора изображенного на рис.14.

## 5. ЭЛЕМЕНТЫ ХРАНЕНИЯ - ТРИГГЕРЫ, АСИНХРОН И СИНХРОН RS-ТРИГГЕРЫ. D-ТРИГГЕР, T-ТРИГГЕР И УНИВЕРСАЛЬНЫЙ JK-ТРИГГЕР

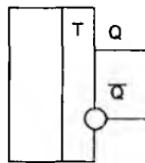

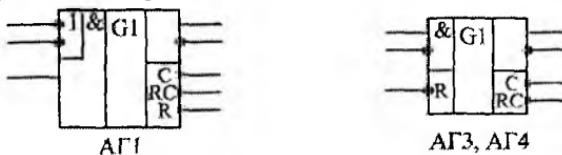

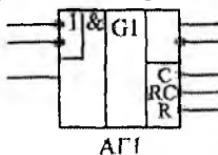

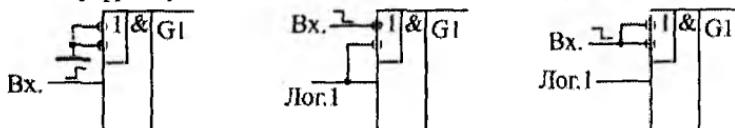

**Общие сведения.** Триггером называется устройство, имеющие два устойчивых состояния («0» или «1») и способные под действием входного сигнала скачком переходить из одного устойчивого состояния в другое.

Триггер – это простейший автомат с памятью и способностью хранить 1 бит информации («0» или «1»).

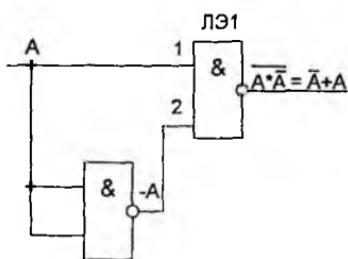

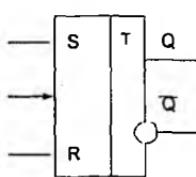

Если выходные сигналы логических элементов (ЛЭ) однозначно определяются их текущими входными сигналами, то выходные сигналы микросхем с внутренней памятью зависят также еще и от того, какие входные сигналы и в какой последовательности поступали на них в прошлом, то есть они помнят предысторию поведения схемы. Микросхемы с внутренней памятью называются еще последовательными. Триггеры имеют два выхода: прямой ( $Q$ ) и инверсный ( $\bar{Q}$ ) (Рис.23.). Если триггер имеет состояние «1», то его выход  $Q$  равен «1», а выход  $\bar{Q}$  равен «0». Если триггер имеет состояние «0», то его выход  $Q$  равен «0», а выход  $\bar{Q}$  равен «1». Число входов зависит от структуры и функций, выполняемых триггером. В основе любого триггера находится регенеративное кольцо из двух инверторов (Рис.24.).

Рис.23. Выходы триггера

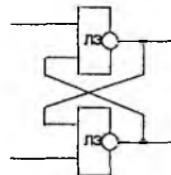

Рис.24. Регенеративное кольцо

внутри триггера

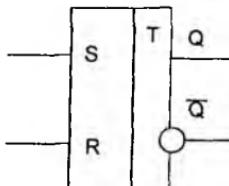

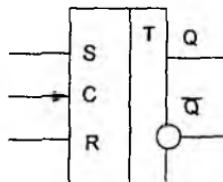

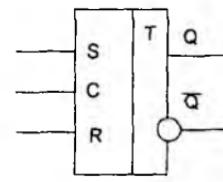

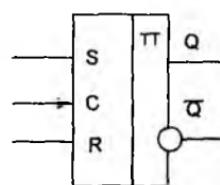

По способу записи информации триггеры делятся на асинхронные и синхронные. У асинхронных триггеров запись информации происходит под действием информационных сигналов. Такие триггеры имеют только информационные входы (Рис.25.). У синхронных триггеров запись информации происходит под действием разрешающих сигналов синхронизации (Рис.26.).

Рис.25. Асинхронный триггер

Рис.26. Синхронный динамический триггер

Рис.27. Синхронный статический триггер

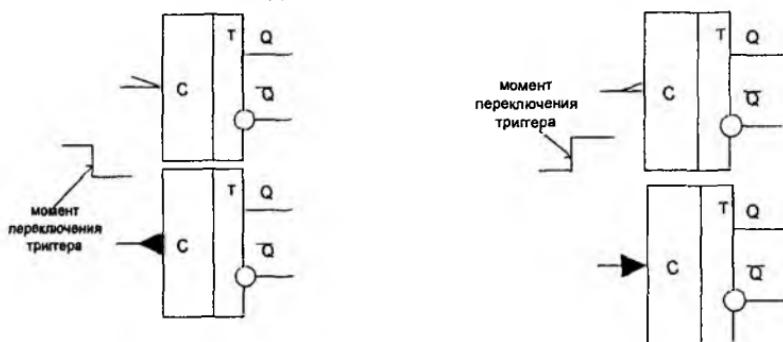

Синхронные триггеры бывают со статическим, динамическим управлением записи и двухступенчатые.

Синхронные триггеры со статическим управлением записью принимают информационные сигналы все время пока действует импульс синхронизации (Рис.27). Следовательно, переключение триггера за время действия импульса синхронизации может быть многократным. У таких триггеров вход С – статический.

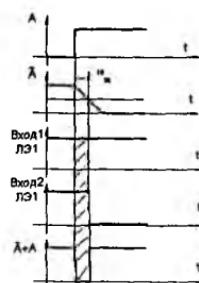

Синхронные триггеры с динамическим управлением записью принимают только информационные сигналы, которые были на информационных входах к моменту прихода синхроимпульса. У таких триггеров вход С – динамический.

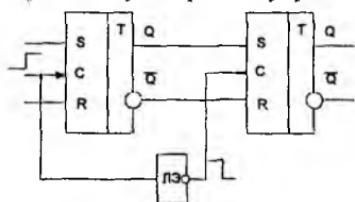

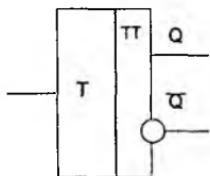

Синхронные двухступенчатые триггеры состоят из двух ступеней (рис.28). Запись информации в первую ступень происходит с появлением синхроимпульса, А во вторую ступень – после окончания синхроимпульса. Следовательно, двухступенчатые триггеры задерживают выходную информацию на время, равное длительности синхроимпульса. Такие триггеры еще называют триггерами с внутренней задержкой.

а) Структура двухступенчатого триггера

б) Условное обозначение двухступенчатого триггера

Рис.28. Синхронный двухступенчатый триггер

Приняты следующие обозначения входов триггеров:

S – раздельный вход установки триггера в единичное состояние по прямому выходу Q;

R – раздельный вход сброса триггера в нулевое состояние по прямому выходу Q;

D – информационный вход. На него подается информация, предназначенная для записи в триггер;

C – вход синхронизации. На Рис.29. приведены условные обозначения входа синхронизации;

T – счетный вход.

Рис.29. Условные обозначения входа синхронизации

**Параметры триггера.** Для всех триггеров характерны следующие параметры:

$K_{\text{раз}}$  - коэффициент разветвления, который показывает нагрузочную способность триггера, т.е. обозначает количество элементов, которые параллельно подсоединены к выходу триггера и на которые подается выходной сигнал триггера.

$K_{\text{об}}$  - коэффициент объединения по входу, который обозначает максимальное число входных сигналов которые можно подать на вход триггера.

$t_u$  - наименьшая длительность входного сигнала (импульса), при котором еще происходит надежное переключение триггера.

$t_{\text{зд}}$  – время задержек между моментом подачи входного и появлением выходного сигнала.

$t_p$  – время разрешения, которое характеризует наименьший интервал между моментами подачи двух входных сигналов с длительностью  $t_u$ , вызывающих переключение триггера.

Принцип работы асинхронного триггера. В основе любого триггера лежит схема из двух логических элементов, которые охвачены положительными обратными связями (то есть сигналы с выходов подаются на входы). В результате подобного включения схема может находиться в одном из двух устойчи-

вых состояний, причем находится сколь угодно долго, пока на нее подано напряжение питания. Пример такой схемы (так называемой триггерной ячейки) на двух двухходовых элементах И-НЕ представлен на Рис. 30. У схемы есть два инверсных входа:

- R - сброс (от английского Reset),

- S - установка (от английского Set).

Схема имеет два выхода: прямой выход Q и инверсный выход -Q.

Согласно определению, триггер может находиться в конкретный момент времени в одном из состояний «0» или «1». Следовательно для правильной работы схемы отрицательные импульсы не должны поступать на ее входы (-S и -R) одновременно.

Рис.30. Схема триггерной ячейки

Рис.31. Диаграмма работы триггерной ячейки

Т.е. если на вход -S подается отрицательный импульс (триггер устанавливается в состояние «1» по прямому выходу Q), то в этот момент времени на вход -R должен подаваться положительный импульс.

Диаграмма работы триггерной ячейки представлена на рис.31.

В начальный момент времени на входы -S и -R действуют сигналы «1», триггерная ячейка находится в состоянии «0» (выход Q = 0, выход -Q=1). В момент, когда на вход -S действует активный сигнал нуля, выход Q триггера перебрасывается в состояние «1» с задержкой на время  $t_{1\text{н}}$  (задержка переключения верхнего элемента), по обратной связи сигнал Q поступает на вход нижнего ЛЭ и вызывает переключение выхода триггера -Q в состояние «0» с задержкой  $t_{1\text{в}}$  (задержка переключения нижнего элемента).

После окончания импульса на входе - S состояние схемы не изменяется (на Q остается единица, на -Q остается ноль). Если триггер стоит в «1» и на

вход – S поступит «0» (на входе –R единица), то триггер останется в состоянии «1».

Точно так же при приходе импульса на вход –R выход –Q устанавливается в единицу, а выход Q — в нуль.

Оба эти устойчивых состояния триггерной ячейки могут сохраняться сколь угодно долго, пока не придет очередной входной импульс.

Следовательно сигналы на выходах триггера устанавливаются спустя время  $t_{\text{зл,тр}} = t_{\text{зл}}^{01} + t_{\text{зл}}^{10}$ . Из временной диаграммы следует, что длительность входных сигналов должна удовлетворять условию  $t_c > t_{\text{зл,тр}}$ . Работу данной триггерной ячейки можно описать таблицей истинности (таблица 1), где

$t$  - момент времени действия входных сигналов S и R;

$t+1$  - момент времени наступающий, когда сигналы на входе схемы под воздействием входных сигналов принимают значения, соответствующие следующему состоянию Q;

$Q^t$  - внутренний сигнал обратной связи (состояние триггера до действия входных сигналов в момент времени  $t+1$ ).

Таблица 1

| $-S^t$ | $-R^t$ | $Q^t$ | $Q^{t+1}$ | Примечание                                                                                                         |

|--------|--------|-------|-----------|--------------------------------------------------------------------------------------------------------------------|

| 0      | 0      | 0     | -         | Запрещенная комбинация                                                                                             |

| 0      | 1      | 0     | 1         | Установка в состояние «1» (триггер стоял в состояние «0», устанавливается в состояние «1» по активному входу – S)  |

| 1      | 0      | 0     | 0         | Установка в состояние «0» (триггер стоял в состояние «0» и устанавливается в состояние «0» по активному входу – R) |

| 1      | 1      | 0     | 0         | Хранение «0» (сигналы на входах неактивны)                                                                         |

| 0      | 0      | 1     |           | Запрещенная комбинация                                                                                             |

| 0      | 1      | 1     |           | Установка в состояние «1» (триггер стоял в состояние «1» и устанавливается в состояние «1» по активному входу – S) |

| 1      | 0      | 1     |           | Установка в состояние «0» (триггер стоял в состояние «0» и устанавливается в состояние «0» по активному входу – R) |

| 1      | 1      | 1     |           | Хранение «1»                                                                                                       |

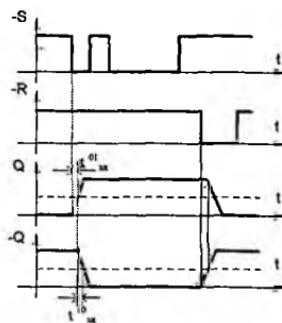

Рис. 32. Условное обозначение триггера R-S

Если оба входных импульса ( $\ll 0$ ) придут одновременно, то в момент действия этих импульсов на обоих выходах будут единичные сигналы - триггерная ячейка находится одновременно в состоянии  $\ll 0$  и  $\ll 1$ , что недопустимо. После окончания входных импульсов выходы случайным образом попадут в одно из двух устойчивых состояний, что не позволит гарантировать корректную работу цифрового устройства.

Случайным образом будет выбрано одно из двух устойчивых состояний триггерной ячейки при включении питания. Триггер, представленный на Рис.4.9. называется -R-S (неRneS) триггером, условное обозначение которого приведено на рис. 32. Длительность сигналов  $-R$  и  $-S$  не должна быть слишком малой, иначе триггер может на них не реагировать. Сигнал  $-R$  должен начинаться с определенной задержкой после окончания сигнала  $-S$ , и наоборот. В первом приближении можно считать, что минимально допустимые временные интервалы между входными сигналами должны равняться 1–2 задержкам логического элемента соответствующей серии.

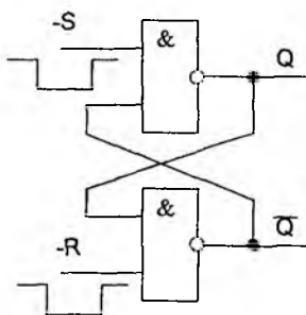

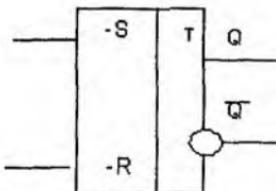

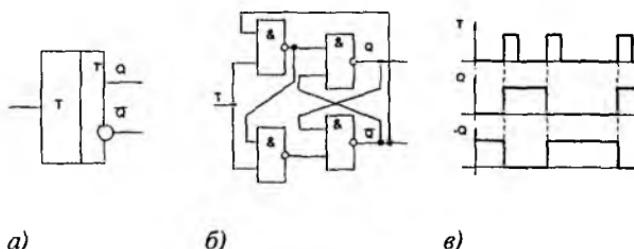

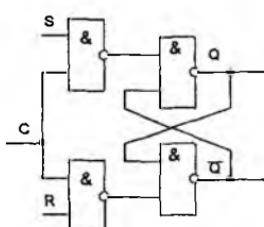

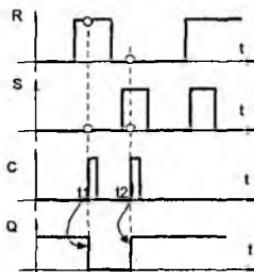

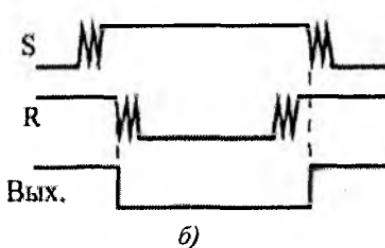

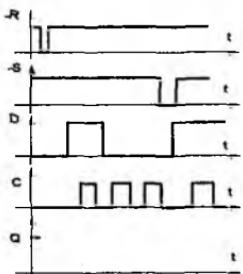

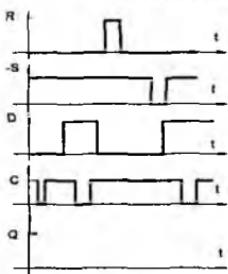

**Асинхронный RS триггер.** Условное обозначение асинхронного RS триггера (а), его схема (б) и диаграмма работы (в) представлены на рис.33. Из схемы и диаграммы работы RS триггера видно, что активным сигналом, вызывающим переключение триггера, например, из состояния  $\ll 1$  в состояние  $\ll 0$  является сигнал  $\ll 1$ . Т.о. запрещенной комбинацией будет являться комбинация входных сигналов  $R=S=1$ .

Рис.33 Условное обозначение асинхронного RS триггера (а),

его схема (б),диаграмма работы (в)

Работу асинхронного RS триггера можно описать таблицей истинности (таблица 4.2).

Таблица 2.

| S <sup>t</sup> | R <sup>t</sup> | Q <sup>t</sup> | Q <sup>t+1</sup> | Примечание                                                                                                        |

|----------------|----------------|----------------|------------------|-------------------------------------------------------------------------------------------------------------------|

| 0              | 0              | 0              | 0                | Хранение «0» (сигналы на входах неактивны)                                                                        |

| 0              | 1              | 0              | 0                | Установка в состояние «0» (триггер стоял в состояние «0», устанавливается в состояние «0» по активному входу R=1) |

| 1              | 0              | 0              | 1                | Установка в состояние «1» (триггер стоял в состояние «0», устанавливается в состояние «1» по активному входу S=1) |

| 1              | 1              | 0              | -                | Запрещенная комбинация                                                                                            |

| 0              | 0              | 1              | 1                | Хранение «1» (сигналы на входах неактивны)                                                                        |

| 0              | 1              | 1              | 0                | Установка в состояние «0» (триггер стоял в состояние «1», устанавливается в состояние «0» по активному входу R=1) |

| 1              | 0              | 1              | 1                | Установка в состояние «1» (триггер стоял в состояние «1», устанавливается в состояние «1» по активному входу S=1) |

| 1              | 1              | 1              | -                | Запрещенная комбинация                                                                                            |

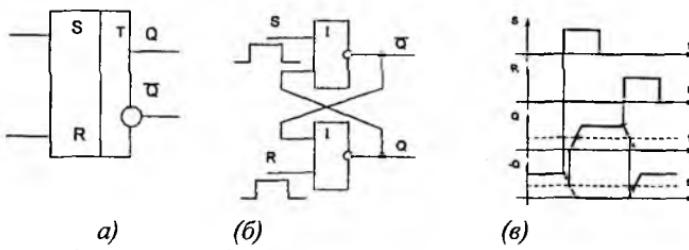

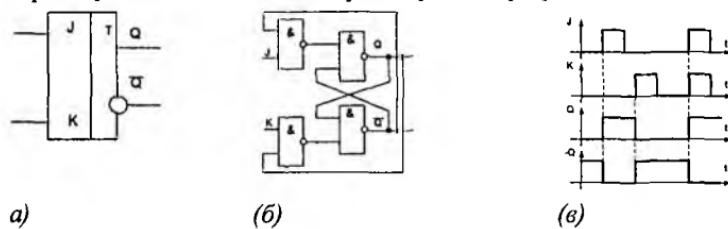

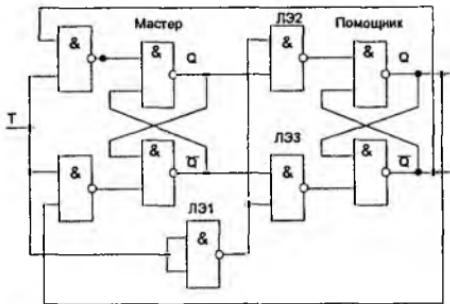

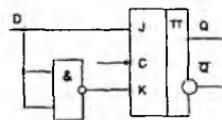

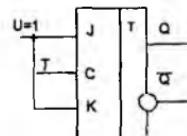

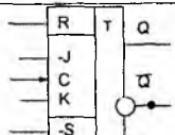

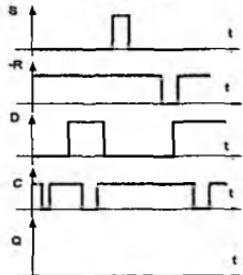

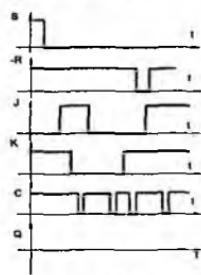

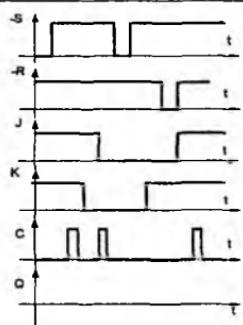

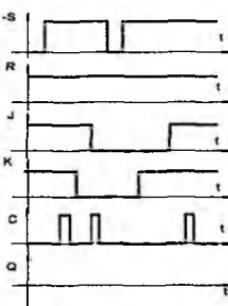

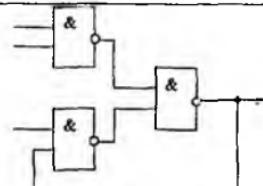

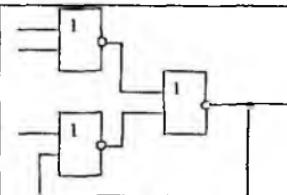

**Асинхронный JK триггер.** Условное обозначение асинхронного JK триггера (а), его схема (б) и диаграмма работы (в) представлены на Рис.34. Особенностью JK триггера является то, что он не имеет запрещенных комбинаций. Если на входы J и K действует активный сигнал («1»), то триггер изменяет свое состояние на противоположное тому, в котором он находился до действия сигналов, иначе говоря работает в счетном режиме.

Вход J триггера (аналогично входу S) является входом установки триггера в единичное состояние по прямому выходу Q.

Вход S триггера (аналогично входу R) является входом установки триггера в нулевое состояние по прямому выходу Q.

Рис.34. Условное обозначение асинхронного JK триггера (а), его схема (б) и диаграмма работы (в)

Работа асинхронного JK триггера можно описать таблицей истинности (таблица 3).

Таблица 3.

| J | K | $Q^t$ | $Q^{t+1}$ | Примечание                                                                                                        |

|---|---|-------|-----------|-------------------------------------------------------------------------------------------------------------------|

| 0 | 0 | 0     | 0         | Хранение «0» (сигналы на входах неактивны)                                                                        |

| 0 | 1 | 0     | 0         | Установка в состояние «0» (триггер стоял в состояние «0», устанавливается в состояние «0» по активному входу K=1) |

| 1 | 0 | 0     | 1         | Установка в состояние «1» (триггер стоял в состояние «0», устанавливается в состояние «1» по активному входу J=1) |

| 1 | 1 | 0     | 1         | Счетный режим, триггер переходит из состояния «0» в состояние «1»                                                 |

| 0 | 0 | 1     | 1         | Хранение «1» (сигналы на входах неактивны)                                                                        |

| 0 | 1 | 1     | 0         | Установка в состояние «0» (триггер стоял в состояние «1», устанавливается в состояние «0» по активному входу K=1) |

| 1 | 0 | 1     | 1         | Установка в состояние «1» (триггер стоял в состояние «1», устанавливается в состояние «1» по активному входу J=1) |

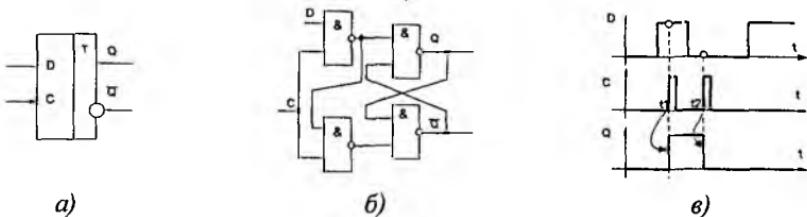

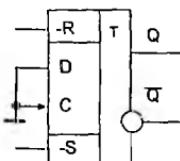

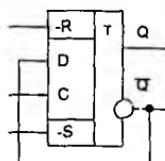

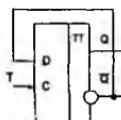

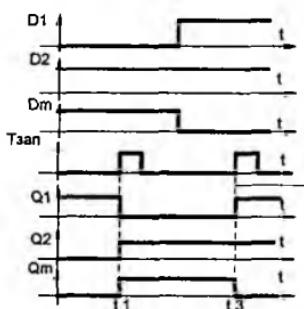

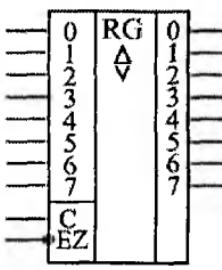

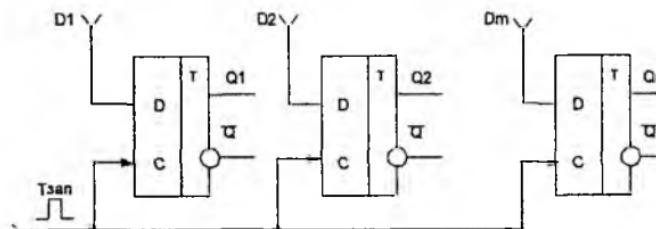

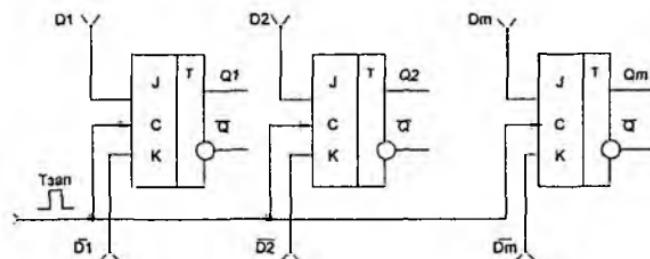

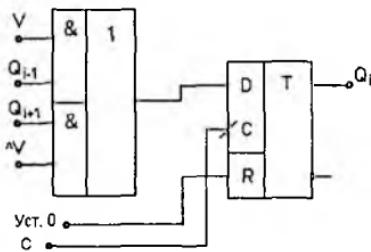

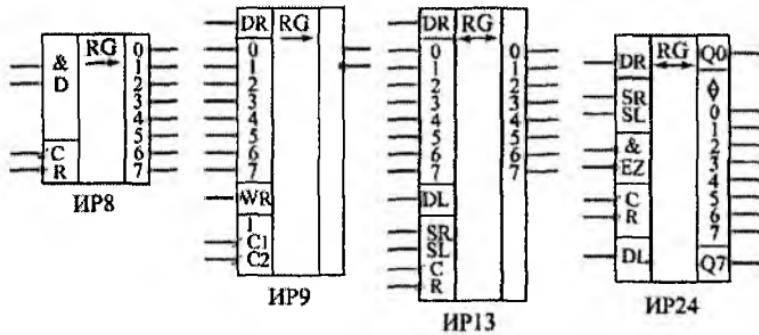

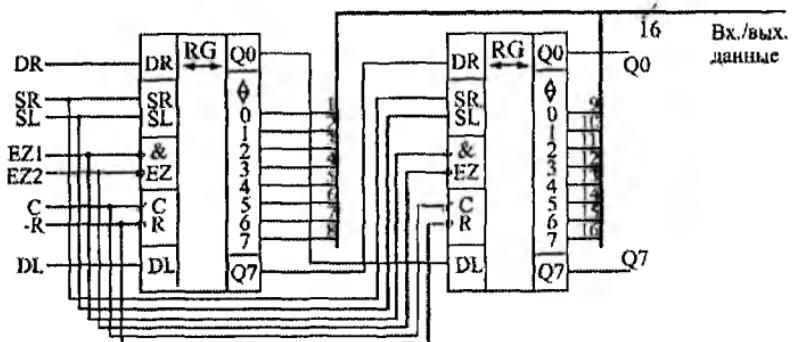

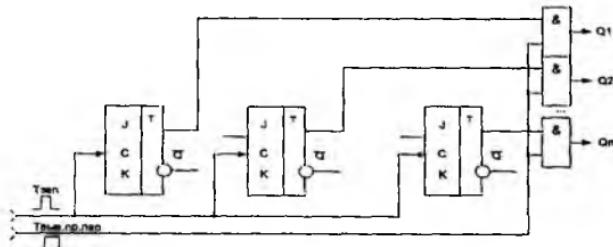

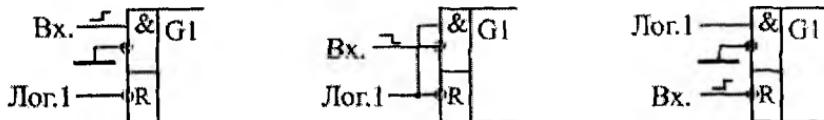

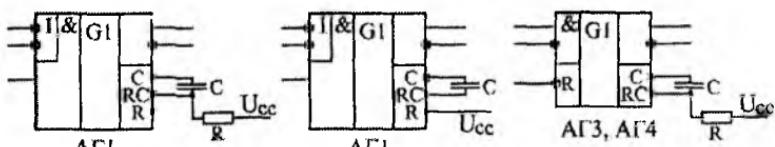

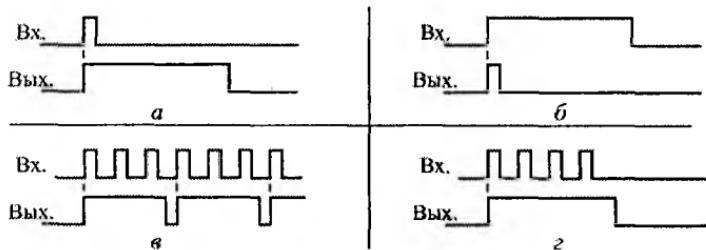

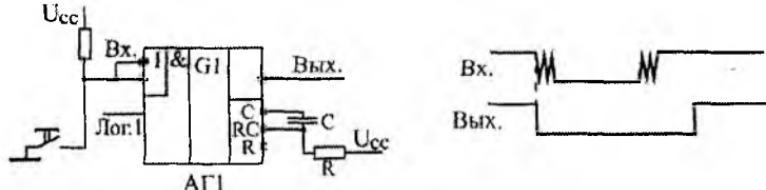

| 1 | 1 | 1     | 0         | Счетный режим, триггер переходит из состояния «1» в состояние «0»                                                 |